Звіт про ринок мікроелектронної упаковки з укладеними чіпами на 2025 рік: зростання, технологічні зміни та стратегічні висновки на наступні 5 років. Досліджуйте ключові тенденції, прогнози та конкурентну динаміку, що формує індустрію.

- Резюме та огляд ринку

- Ключові технологічні тенденції в упаковці з укладеними чіпами мікроелектроніки

- Конкурентне середовище та провідні гравці

- Прогнози зростання ринку (2025–2030): CAGR, аналіз доходів та обсягів

- Регіональний аналіз ринку: Північна Америка, Європа, Азійсько-Тихоокеанський регіон та інші країни

- Перспективи: нові застосування та інвестиційні точки

- Виклики, ризики та стратегічні можливості

- Джерела та посилання

Резюме та огляд ринку

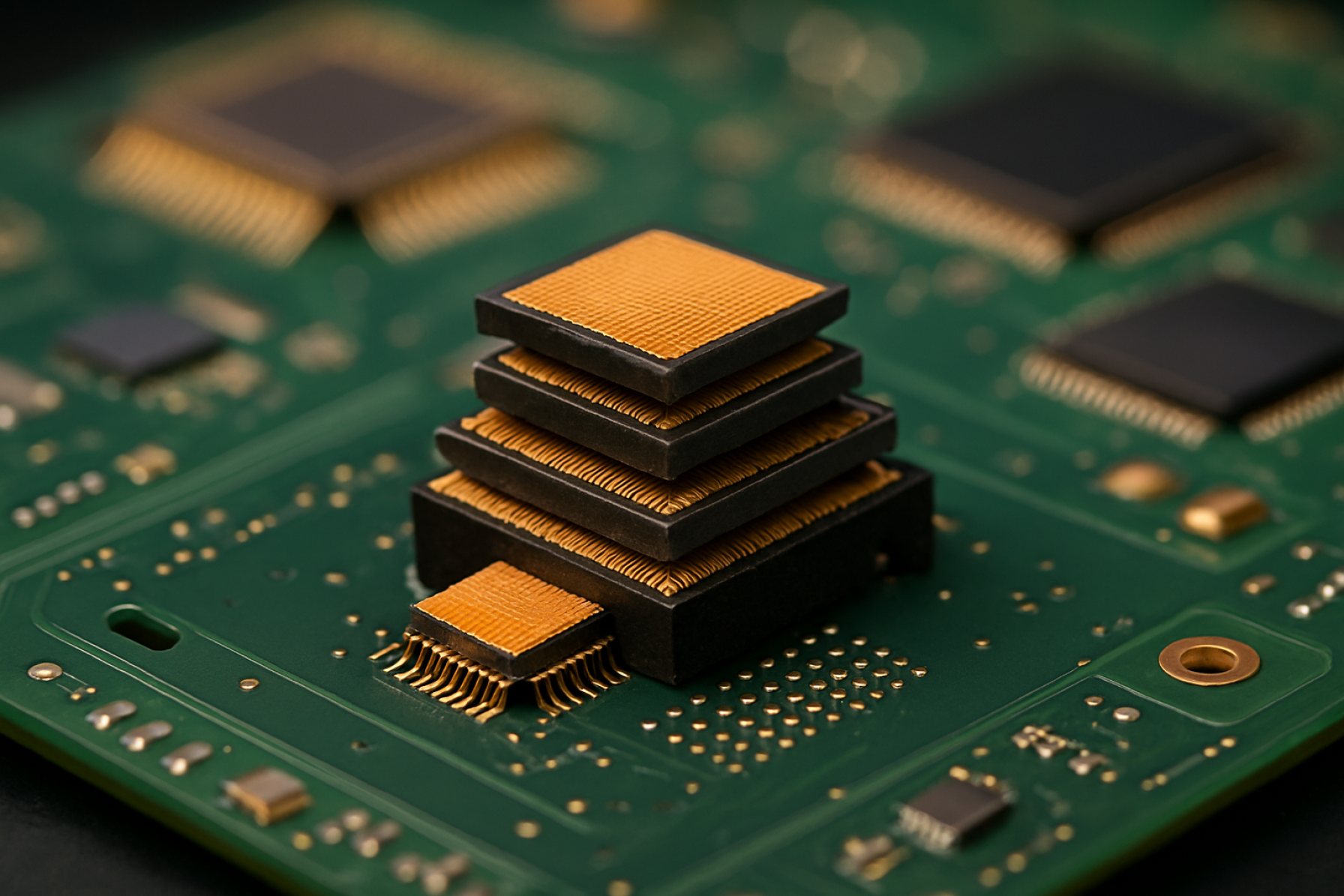

Упаковка з укладеними чіпами мікроелектроніки відноситься до інтеграції кількох напівпровідникових чіпів в одній упаковці, розташованій вертикально для оптимізації простору, продуктивності та функціональності. Ця розвинута технологія упаковки є ключовою для задоволення зростаючих вимог до мініатюризації, вищої продуктивності та енергетичної ефективності в таких секторах, як споживча електроніка, автомобілебудування, телекомунікації та центри обробки даних. Станом на 2025 рік світовий ринок упаковки з укладеними чіпами мікроелектроніки демонструє сильне зростання, зумовлене поширенням 5G пристроїв, застосувань штучного інтелекту (ШІ) та інтернету речей (IoT).

Згідно з даними Yole Group, ринок розвинутої упаковки, до якого входять рішення з укладеними чіпами, імовірно, досягне понад 50 мільярдів доларів США до 2025 року, причому архітектури з укладеними чіпами займають значну частку через їх використання в продуктивній логіці, пам’яті та гетерогенної інтеграції. Попит на пам’ять високої пропускної здатності (HBM), 3D NAND та рішення в упаковці системи (SiP) підсилює перехід до конфігурацій з укладеними чіпами, оскільки вони забезпечують вищу щільність з’єднань та поліпшену електричну продуктивність у порівнянні з традиційною 2D упаковкою.

Ключові гравці індустрії, такі як TSMC, Samsung Electronics та Intel Corporation, активно інвестують у наукові дослідження та розробки, щоб просунути технології черезсиликонових з’єднань (TSV) та упаковки на рівні кристала (WLP), які є основою для інтеграції укладених чіпів. Ці інновації дозволяють виробляти менші, швидші та більш енергоефективні пристрої, особливо в сферах високопродуктивних обчислень та мобільних додатків.

Регіонально, Азійсько-Тихоокеанський регіон домінує на ринку упаковки з укладеними чіпами мікроелектроніки, зосереджуючи виробництво в Тайвані, Південній Кореї та Китаї. Регіон користується сильною ланцюгом постачання напівпровідників і активними інвестиціями в підприємства з упаковки наступного покоління. Північна Америка та Європа також спостерігають за зростанням прийняття, особливо в автомобільній електроніці та інфраструктурі центрів обробки даних, де рішення з укладеними чіпами є критично важливими для задоволення суворих вимог до продуктивності та надійності.

Оглядаючи 2025 рік, очікується, що ринок упаковки з укладеними чіпами мікроелектроніки збережеться на рівні двозначного складного річного темпу зростання (CAGR), підживлюється триваючими технологічними вдосконаленнями та неперервним прагненням до мініатюризації пристроїв. Однак виклики, такі як управління теплом, оптимізація виходу та обмеження в ланцюгу постачань, залишаються пріоритетними питаннями для учасників ринку, які прагнуть скористатися цим динамічним сегментом ринку.

Ключові технологічні тенденції в упаковці з укладеними чіпами мікроелектроніки

Упаковка з укладеними чіпами мікроелектроніки перебуває на передньому краї інновацій у галузі напівпровідників, дозволяючи досягати вищої продуктивності пристроїв, підвищувати функціональність та зменшувати розміри завдяки вертикальному інтегруванню кількох напівпровідникових чіпів в одній упаковці. Оскільки індустрія переходить у 2025 рік, кілька ключових технологічних тенденцій формують еволюцію та споживання рішень з укладеними чіпами.

- Розвинена інтеграція черезсиликонових з’єднань (TSV): Технологія TSV залишається центральною для архітектур з укладеними чіпами, забезпечуючи високощільні вертикальні з’єднання. Останні вдосконалення зосереджені на зменшенні діаметра та кроку з’єднань, що покращує цілісність сигналу та енергоефективність. Провідні фабрики, такі як TSMC та Samsung Electronics, активно підвищують масштаби TSV, щоб підтримати пам’ять високої пропускної здатності (HBM3) та інтеграцію логіки з пам’яттю для застосувань ШІ та HPC.

- Гетерогенна інтеграція: Тенденція до інтеграції різноманітних чіплетів — логіки, пам’яті, аналогових та RF — в одну укладену упаковку пришвидшується. Цей підхід дозволяє оптимізацію на рівні системи та підтримує зростаючий попит на спеціалізовані інтегровані схеми (ASIC) в центрах обробки даних, автомобільній техніці та мобільних пристроях. Foveros від Intel та 3D V-Cache від AMD є прикладами комерційного прийняття гетерогенного укладання.

- Упаковка на рівні кристала (WLP) та технології фан-аут: Упаковка на рівні кристала та фан-аут панельна упаковка набирають популярність через свою здатність забезпечувати тонші інтерконектні кроки та поліпшену теплову продуктивність. ASE Technology Holding та Amkor Technology інвестують у розвинені лінії WLP, щоб задовольнити попит на компактну, високо продуктивну споживчу та автомобільну електроніку.

- Інновації в управлінні теплом: Оскільки продуктивність енергії зростає, ефективне розсіювання тепла стає критично важливим. Нові матеріали (наприклад, діамантові композити, просунуті TIM) та інтегроване мікрофлюїдне охолодження вивчаються для подолання теплових вузьких місць в упаковках з укладеними чіпами, про що йдеться в останніх звітах ринку Yole Group.

- Автоматизація проектування та тестові рішення: Складність архітектур з укладеними чіпами сприяє прийняттю розвинених інструментів автоматизації електронного проектування (EDA) та методологій самоперевірки (BIST). Компанії, такі як Synopsys та Cadence Design Systems, розробляють рішення для спрощення проектування 3D IC, верифікації та оптимізації виходу.

Ці технологічні тенденції очікується прискорять прийняття упаковки з укладеними чіпами мікроелектроніки у 2025 році, підтримуючи наступне покоління застосувань в AI, 5G, автомобільній техніці та обчисленнях на краю.

Конкурентне середовище та провідні гравці

Конкурентне середовище ринку упаковки з укладеними чіпами мікроелектроніки у 2025 році характеризується інтенсивними інноваціями, стратегічними партнерствами та акцентом на просунуті технології інтеграції. Упаковка з укладеними чіпами, яка дозволяє вертикальну інтеграцію кількох напівпровідникових чіпів в одній упаковці, є критичним фактором для високопродуктивних обчислень, мобільних пристроїв та нових застосувань, таких як штучний інтелект (ШІ) та 5G комунікації.

Провідними гравцями на цьому ринку є Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation та Amkor Technology. Ці компанії зарекомендували себе як піонери в розвинутих рішеннях упаковки, використовуючи свій досвід у виготовленні кристалів, 3D інтеграції та технологіях системи в упаковці (SiP).

TSMC продовжує лідирувати завдяки своїм просунутим платформам 3D упаковки, таким як CoWoS (Chip-on-Wafer-on-Substrate) та SoIC (System on Integrated Chips), які широко використовуються для високопродуктивних обчислень і прискорювачів AI. Samsung Electronics досягла значних успіхів зі своєю технологією X-Cube (eXtended-Cube), що забезпечує інтеграцію пам’яті високої щільності та високої пропускної здатності для мобільних та серверних програм наступного покоління. Intel вдосконалює свою технологію 3D укладання Foveros, що дозволяє гетерогенну інтеграцію чіпів логіки та пам’яті, підтримуючи прагнення компанії в ринки AI та центрів обробки даних.

Аутсорсингові постачальники зборки напівпровідників та тестування (OSAT), такі як Amkor Technology та ASE Technology Holding, також ключові гравці, що пропонують широкий портфель послуг з упаковки з укладеними чіпами для безкристальних напівпровідникових компаній та інтегрованих виробників пристроїв (IDM). Ці OSAT інвестують у розвинуті лінії упаковки та співпрацюють з фабриками, щоб прискорити вихід на ринок для комплексних рішень з кількома чіпами.

- TSMC: Лідерство в платформах CoWoS та SoIC для AI та HPC.

- Samsung Electronics: Технологія X-Cube для інтеграції пам’яті високої пропускної здатності.

- Intel Corporation: 3D укладання Foveros для гетерогенної інтеграції.

- Amkor Technology та ASE Technology Holding: Розвинуті OSAT послуги для рішень з укладеними чіпами.

Оскільки зростає попит на мініатюризацію та продуктивність, очікується, що конкурентне середовище побачить подальшу консолідацію, оскільки провідні гравці інвестують значні кошти в НДО та екосистемні партнерства, щоб зберегти свою технологічну перевагу в упаковці з укладеними чіпами мікроелектроніки.

Прогнози зростання ринку (2025–2030): CAGR, аналіз доходів та обсягів

Ринок упаковки з укладеними чіпами мікроелектроніки готовий до сильного зростання між 2025 та 2030 роками, завдяки зростаючому попиту на високопродуктивні, мініатюризовані електронні пристрої в секторах, таких як споживча електроніка, автомобілебудування, телекомунікації та охорона здоров’я. Згідно з прогнозами MarketsandMarkets, світовий ринок 3D IC та упаковки з укладеними чіпами очікує зареєструвати складний річний темп зростання (CAGR) приблизно 12–14% протягом цього періоду. Ця траєкторія зростання підкріплюється зростаючим прийняттям розвинутих технологій упаковки для вирішення обмежень традиційних 2D архітектур, зокрема в плані енергоефективності, форм-фактора та пропускної здатності даних.

Прогнози доходів вказують на те, що ринок упаковки з укладеними чіпами мікроелектроніки може перевищити 15 мільярдів доларів США до 2030 року, підвищившись з приблизно 7.5 мільярдів доларів у 2025 році. Цей сплеск пов’язаний з розширенням застосувань, які потребують високощільної інтеграції, таких як прискорювачі штучного інтелекту (AI), інфраструктура 5G та пристрої обчислень на краю. Азійсько-Тихоокеанський регіон, на чолі з Китаєм, Південною Кореєю та Тайванем, очікується, що займе значну частку ринку, становлячи понад 50% світових доходів, завдяки концентрації виробництв напівпровідників і упаковки в цьому регіоні (Gartner).

Що стосується обсягу, то кількість одиниць укладених чіпів, які надходять на ринок, прогнозується, що зросте з CAGR 13–15% з 2025 по 2030 рік. Це розширення обсягу зумовлене швидкою розбіжністю пристроїв наступного покоління, такими як смартфони, пристрої для носіння та автомобільна електроніка, всі з яких потребують компактних, високопродуктивних упаковок. Зокрема, автомобільний сектор прогнозується з найшвидшим зростанням обсягів, оскільки електричні автомобілі (EV) та системи допомоги водіям (ADAS) все більше покладаються на укладені архітектури для покращення обчислювальної потужності та надійності (Yole Group).

- CAGR (2025–2030): 12–14%

- Доходи (2030): >15 мільярдів доларів США

- Обсяг CAGR (2025–2030): 13–15%

- Ключові драйвери зростання: AI, 5G, автомобільна електроніка, мініатюризація

- Провідний регіон: Азійсько-Тихоокеанський регіон

Регіональний аналіз ринку: Північна Америка, Європа, Азійсько-Тихоокеанський регіон та інші країни

Світовий ринок упаковки з укладеними чіпами мікроелектроніки свідчить про динамічне зростання, при цьому регіональні тенденції формуються технологічними досягненнями, попитом кінцевих споживачів і розвитком ланцюгів постачання. У 2025 році ринки Північної Америки, Європи, Азійсько-Тихоокеанського регіону та інших країн мають свої унікальні характеристики та драйвери зростання.

- Північна Америка: Північноамериканський ринок підштовхується до активних інвестицій у розвинуте виробництво напівпровідників та сильну присутність провідних технологічних компаній. Фокус регіону на високопродуктивних обчисленнях, інфраструктурі 5G та автомобільній електроніці стимулює попит на рішення з упаковки з укладеними чіпами. Сполучені Штати, зокрема, отримують вигоду від урядових ініціатив для зміцнення продукції чипів у країні, як це видно в Законі CHIPS, який, як очікується, прискорить прийняття просунутих технологій упаковки у 2025 році (Ассоціація індустрії напівпровідників).

- Європа: Ринок упаковки з укладеними чіпами мікроелектроніки в Європі характеризується фокусом на автомобільні, промислові автоматизаційні та IoT програми. Прагнення регіону до технологічного суверенітету та Європейський Закон про чипи сприяють інвестиціям у місцеві екосистеми напівпровідників. Німеччина та Франція лідирують у НДО та пілотному виробництві з акцентом на енергоефективні та мініатюризовані пристрої (Європейська асоціація виробників електронних компонентів).

- Азійсько-Тихоокеанський регіон: Азійсько-Тихоокеанський регіон залишається найбільшим та найшвидше зростаючим ринком упаковки з укладеними чіпами, завдяки домінуванню країн, таких як Китай, Південна Корея, Тайвань та Японія в виготовленні та складанні напівпровідників. Поширення споживчої електроніки, смартфонів та пристроїв на основі AI сприяє збільшенню попиту. Основні фабрики та постачальники OSAT (Аутсорсингові постачальники зборки напівпровідників та тестування) в регіоні нарощують інвестиції в упаковку 2.5D/3D та гетерогенну інтеграцію для задоволення глобального попиту (SEMI).

- Інші країни (RoW): Хоча менший за масштабом, сегмент RoW — включаючи Латинську Америку, Близький Схід та Африку — поступово впроваджує упаковку з укладеними чіпами, головно для телекомунікацій та нових промислових Anwendung. Зростання підтримується зростаючою цифровізацією та урядовими технологічними ініціативами, хоча регіон стикається з викликами, пов’язаними з інфраструктурою та кваліфікованою робочою силою (Gartner).

Перспективи: нові застосування та інвестиційні точки

Нові застосування особливо яскраво проявляються в центрах обробки даних, інфраструктурі 5G та обчисленнях на краю. Потреба в більшій пропускній здатності та нижчій затримці в цих середовищах підштовхує до впровадження рішень з 2.5D та 3D укладеними чіпами, які пропонують поліпшену щільність з’єднань та зменшену втрату сигналу в порівнянні з традиційною упаковкою. Наприклад, центри обробки даних гіпермасштабів все більше використовують пам’ять високої пропускної здатності (HBM) та укладення логіки в пам’яті для прискорення завдань AI та аналітики великих даних, що підкреслюється останніми аналізами від Gartner та IDC.

Споживча електроніка, особливо смартфони та пристрої для носіння, залишаються важливою інвестиційною точкою. Прагнення до тонших, легших пристроїв з розширеною функціональністю стимулює попит на розвинені технології упаковки, такі як черезсиликонові з’єднання (TSV) та укладення на рівні кристала. За даними Yole Group, ринок упаковки з укладеними чіпами в мобільних та IoT пристроях очікується на зростання двозначним темпом через 2025 рік, оскільки OEMи намагаються інтегрувати більше функцій без збільшення площі пристрою.

Автомобільна електроніка є ще однією новою областю застосування, особливо оскільки електричні транспортні засоби (EV) та системи автономного водіння вимагатимуть компактних, високонадійних обчислювальних модулів. Упаковка з укладеними чіпами дозволяє інтегрувати сенсори, процесори та пам’ять в один модуль, що підтримує обробку даних в реальному часі та системи допомоги водіям (ADAS). McKinsey & Company прогнозує, що зміст напівпровідників в автомобільній техніці перевищить загальне зростання автомобілів, з рішеннями з укладеними чіпами, які відіграють центральну роль.

- Ключові інвестиційні можливості на 2025 рік включають розвинену пам’ять (HBM, 3D NAND), прискорювачі AI, базові станції 5G/6G та модулі ADAS для автомобілів.

- Азійсько-Тихоокеанський регіон, зокрема Тайвань та Південна Корея, очікується, що домінуватиме у виробництві та інвестиціях у НДО, як зазначено SEMI.

- Стратегічне партнерство між фабриками, OSAT та системними інтеграторами прискорює інновації та комерціалізацію технологій укладених чіпів.

Підсумовуючи, упаковка з укладеними чіпами мікроелектроніки готова стати основою критичних досягнень у обчисленнях, з’єднанні та мобільності у 2025 році, з потужними інвестиціями та інноваціями, зосередженими на високозростаючих, високовартісних секторах застосування.

Виклики, ризики та стратегічні можливості

Упаковка з укладеними чіпами мікроелектроніки, критично важлива для високощільних, високопродуктивних електронних систем, стикається з складним ландшафтом викликів та ризиків у 2025 році, але також представляє значні стратегічні можливості для учасників галузі. Основну технічну проблему становить управління теплом. Оскільки все більше чіпів інтегрується вертикально, розсіювання тепла стає все більш проблематичним, що може призвести до ризиків надійності та зниження продуктивності пристроїв. Досліджуються просунуті температурні інтерфейсні матеріали та інноваційні рішення для розподілу тепла, але їх інтеграція додає витрат та складності до процесу виробництва (SEMI).

Ризики виходу та надійності також посилюються в архітектурах з укладеними чіпами. Збільшення кількості з’єднань, таких як черезсиликонові з’єднання (TSV), підвищує ймовірність дефектів, що впливають на загальний вихід. Більше того, механічні напруження, індуковані під час укладання та упаковки, можуть призводити до тріщин або деламінації чіпа, особливо оскільки розміри упаковки зменшуються, а кількість чіпів зростає. Ці проблеми з надійністю вимагають суворих протоколів тестування та перевірки, що може подовжити терміни виходу на ринок та збільшити витрати (Yole Group).

Складність у ланцюзі постачання також є значним ризиком. Упаковка з укладеними чіпами часто вимагає співпраці між кількома постачальниками для виготовлення кристалів, зменшення чіпів, укладання та остаточної збірки. Порушення в будь-якому сегменті — такі як дефіцит передових підкладок або затримки в обладнанні для прецизійного з’єднання — можуть призвести до затримок у виробництві. Поточні геополітичні напруження та дефіцити матеріалів, які спостерігалися в останні роки, підкреслили вразливість цих складних ланцюгів постачання (Gartner).

Незважаючи на ці виклики, стратегічні можливості процвітають. Зростаючий попит на пам’ять високої пропускної здатності, прискорювачі ШІ та інфраструктура 5G/6G стимулює інвестиції в рішення з укладеними чіпами. Компанії, які можуть інвестувати в такі сфери, як гетерогенна інтеграція, архітектури чіплетів та просунуте управління теплом, можуть захопити значну частку ринку. Стратегічні партнерства між фабриками, OSAT та постачальниками EDA інструментів виникають як ключовий фактор успіху, забезпечуючи рішення, які відповідають технічним і ризикам ланцюга постачання (TSMC).

Підсумовуючи, хоча упаковка з укладеними чіпами мікроелектроніки у 2025 році піддається технічним, надійнісним та ризикам у ланцюгу постачання, вона також пропонує значні можливості зростання для тих, хто може орієнтуватися в розвиваючому ландшафті з інноваціями та стратегічною співпрацею.

Джерела та посилання

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Ассоціація індустрії напівпровідників

- IDC

- McKinsey & Company