2025 Stacked Die Microelectronics Packaging Market Report: Growth, Technology Shifts, and Strategic Insights for the Next 5 Years. Explore Key Trends, Forecasts, and Competitive Dynamics Shaping the Industry.

- Executive Summary & Market Overview

- Key Technology Trends in Stacked Die Microelectronics Packaging

- Competitive Landscape and Leading Players

- Market Growth Forecasts (2025–2030): CAGR, Revenue, and Volume Analysis

- Regional Market Analysis: North America, Europe, Asia-Pacific, and Rest of World

- Future Outlook: Emerging Applications and Investment Hotspots

- Challenges, Risks, and Strategic Opportunities

- Sources & References

Executive Summary & Market Overview

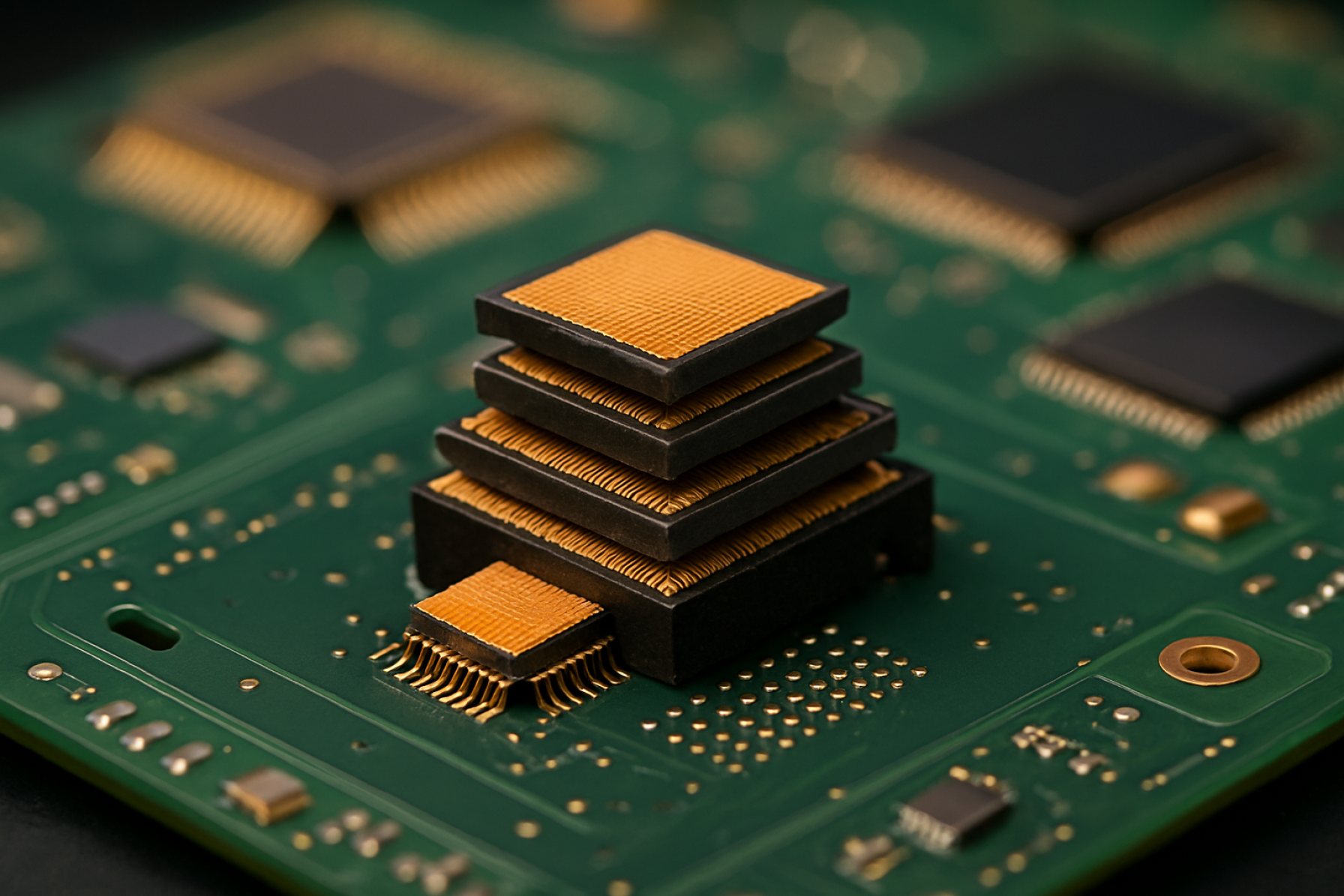

Stacked die microelectronics packaging refers to the integration of multiple semiconductor dies within a single package, arranged vertically to optimize space, performance, and functionality. This advanced packaging technology is pivotal in meeting the escalating demands for miniaturization, higher performance, and energy efficiency in sectors such as consumer electronics, automotive, telecommunications, and data centers. As of 2025, the global market for stacked die microelectronics packaging is experiencing robust growth, driven by the proliferation of 5G devices, artificial intelligence (AI) applications, and the Internet of Things (IoT).

According to Yole Group, the advanced packaging market, which includes stacked die solutions, is projected to reach over $50 billion by 2025, with stacked die architectures accounting for a significant share due to their adoption in high-end logic, memory, and heterogeneous integration. The demand for high-bandwidth memory (HBM), 3D NAND, and system-in-package (SiP) solutions is accelerating the shift toward stacked die configurations, as these enable higher interconnect density and improved electrical performance compared to traditional 2D packaging.

Key industry players such as TSMC, Samsung Electronics, and Intel Corporation are investing heavily in research and development to advance through-silicon via (TSV) and wafer-level packaging (WLP) technologies, which are foundational to stacked die integration. These innovations are enabling the production of smaller, faster, and more power-efficient devices, particularly in high-performance computing and mobile applications.

Regionally, Asia-Pacific dominates the stacked die microelectronics packaging market, led by manufacturing hubs in Taiwan, South Korea, and China. The region benefits from a strong semiconductor supply chain and aggressive investments in next-generation packaging facilities. North America and Europe are also witnessing increased adoption, particularly in automotive electronics and data center infrastructure, where stacked die solutions are critical for meeting stringent performance and reliability requirements.

Looking ahead to 2025, the stacked die microelectronics packaging market is expected to maintain a double-digit compound annual growth rate (CAGR), fueled by ongoing technological advancements and the relentless push for device miniaturization. However, challenges such as thermal management, yield optimization, and supply chain constraints remain focal points for industry stakeholders seeking to capitalize on this dynamic market segment.

Key Technology Trends in Stacked Die Microelectronics Packaging

Stacked die microelectronics packaging is at the forefront of semiconductor innovation, enabling higher device performance, increased functionality, and reduced form factors by vertically integrating multiple semiconductor dies within a single package. As the industry moves into 2025, several key technology trends are shaping the evolution and adoption of stacked die solutions.

- Advanced Through-Silicon Via (TSV) Integration: TSV technology remains central to stacked die architectures, providing high-density vertical interconnects. Recent advancements focus on reducing via diameter and pitch, which enhances signal integrity and power efficiency. Leading foundries such as TSMC and Samsung Electronics are pushing TSV scaling to support high-bandwidth memory (HBM3) and logic-memory integration for AI and HPC applications.

- Heterogeneous Integration: The trend toward integrating diverse chiplets—logic, memory, analog, and RF—within a single stacked package is accelerating. This approach enables system-level optimization and supports the growing demand for application-specific integrated circuits (ASICs) in data centers, automotive, and mobile devices. Intel’s Foveros and AMD’s 3D V-Cache exemplify commercial adoption of heterogeneous stacking.

- Wafer-Level Packaging (WLP) and Fan-Out Technologies: Wafer-level stacking and fan-out panel-level packaging are gaining traction for their ability to deliver finer interconnect pitches and improved thermal performance. ASE Technology Holding and Amkor Technology are investing in advanced WLP lines to meet demand for compact, high-performance consumer and automotive electronics.

- Thermal Management Innovations: As power densities rise, effective heat dissipation becomes critical. New materials (e.g., diamond composites, advanced TIMs) and integrated microfluidic cooling are being explored to address thermal bottlenecks in stacked die packages, as highlighted in recent Yole Group market reports.

- Design Automation and Test Solutions: The complexity of stacked die architectures is driving the adoption of advanced electronic design automation (EDA) tools and built-in self-test (BIST) methodologies. Companies like Synopsys and Cadence Design Systems are developing solutions to streamline 3D IC design, verification, and yield optimization.

These technology trends are expected to accelerate the adoption of stacked die microelectronics packaging in 2025, supporting next-generation applications in AI, 5G, automotive, and edge computing.

Competitive Landscape and Leading Players

The competitive landscape of the stacked die microelectronics packaging market in 2025 is characterized by intense innovation, strategic partnerships, and a focus on advanced integration technologies. Stacked die packaging, which enables the vertical integration of multiple semiconductor dies within a single package, is a critical enabler for high-performance computing, mobile devices, and emerging applications such as artificial intelligence (AI) and 5G communications.

Leading players in this market include Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation, and Amkor Technology. These companies have established themselves as pioneers in advanced packaging solutions, leveraging their expertise in wafer fabrication, 3D integration, and system-in-package (SiP) technologies.

TSMC continues to lead with its advanced 3D packaging platforms, such as CoWoS (Chip-on-Wafer-on-Substrate) and SoIC (System on Integrated Chips), which are widely adopted for high-performance computing and AI accelerators. Samsung Electronics has made significant strides with its X-Cube (eXtended-Cube) technology, enabling high-density, high-bandwidth memory integration for next-generation mobile and server applications. Intel is advancing its Foveros 3D stacking technology, which allows for heterogeneous integration of logic and memory dies, supporting the company’s push into AI and data center markets.

Outsourced semiconductor assembly and test (OSAT) providers such as Amkor Technology and ASE Technology Holding are also key players, offering a broad portfolio of stacked die packaging services to fabless semiconductor companies and integrated device manufacturers (IDMs). These OSATs are investing in advanced packaging lines and collaborating with foundries to accelerate time-to-market for complex multi-die solutions.

- TSMC: Leadership in CoWoS and SoIC platforms for AI and HPC.

- Samsung Electronics: X-Cube technology for high-bandwidth memory integration.

- Intel Corporation: Foveros 3D stacking for heterogeneous integration.

- Amkor Technology and ASE Technology Holding: Advanced OSAT services for stacked die solutions.

As the demand for miniaturization and performance intensifies, the competitive landscape is expected to see further consolidation, with leading players investing heavily in R&D and ecosystem partnerships to maintain their technological edge in stacked die microelectronics packaging.

Market Growth Forecasts (2025–2030): CAGR, Revenue, and Volume Analysis

The stacked die microelectronics packaging market is poised for robust growth between 2025 and 2030, driven by escalating demand for high-performance, miniaturized electronic devices across sectors such as consumer electronics, automotive, telecommunications, and healthcare. According to projections by MarketsandMarkets, the global 3D IC and stacked die packaging market is expected to register a compound annual growth rate (CAGR) of approximately 12–14% during this period. This growth trajectory is underpinned by the increasing adoption of advanced packaging solutions to address the limitations of traditional 2D architectures, particularly in terms of power efficiency, form factor, and data bandwidth.

Revenue forecasts indicate that the stacked die microelectronics packaging market could surpass USD 15 billion by 2030, up from an estimated USD 7.5 billion in 2025. This surge is attributed to the proliferation of applications requiring high-density integration, such as artificial intelligence (AI) accelerators, 5G infrastructure, and edge computing devices. The Asia-Pacific region, led by countries like China, South Korea, and Taiwan, is anticipated to dominate market share, accounting for over 50% of global revenues, owing to the concentration of semiconductor manufacturing and packaging facilities in the region (Gartner).

In terms of volume, the number of stacked die units shipped is projected to grow at a CAGR of 13–15% from 2025 to 2030. This volume expansion is fueled by the rapid rollout of next-generation smartphones, wearables, and automotive electronics, all of which require compact, high-performance packaging solutions. Notably, the automotive sector is expected to witness the fastest volume growth, as electric vehicles (EVs) and advanced driver-assistance systems (ADAS) increasingly rely on stacked die architectures for enhanced computational power and reliability (Yole Group).

- CAGR (2025–2030): 12–14%

- Revenue (2030): >USD 15 billion

- Volume CAGR (2025–2030): 13–15%

- Key Growth Drivers: AI, 5G, automotive electronics, miniaturization

- Leading Region: Asia-Pacific

Regional Market Analysis: North America, Europe, Asia-Pacific, and Rest of World

The global market for stacked die microelectronics packaging is witnessing dynamic growth, with regional trends shaped by technological advancements, end-user demand, and supply chain developments. In 2025, North America, Europe, Asia-Pacific, and the Rest of World (RoW) regions each present distinct market characteristics and growth drivers.

- North America: The North American market is propelled by robust investments in advanced semiconductor manufacturing and a strong presence of leading technology firms. The region’s focus on high-performance computing, 5G infrastructure, and automotive electronics is driving demand for stacked die packaging solutions. The United States, in particular, benefits from government initiatives to bolster domestic chip production, as seen in the CHIPS Act, which is expected to accelerate adoption of advanced packaging technologies in 2025 (Semiconductor Industry Association).

- Europe: Europe’s stacked die microelectronics packaging market is characterized by a focus on automotive, industrial automation, and IoT applications. The region’s push for technological sovereignty and the European Chips Act are fostering investments in local semiconductor ecosystems. Germany and France are leading in R&D and pilot production, with a growing emphasis on energy-efficient and miniaturized devices (European Electronic Component Manufacturers Association).

- Asia-Pacific: Asia-Pacific remains the largest and fastest-growing market for stacked die packaging, driven by the dominance of countries like China, South Korea, Taiwan, and Japan in semiconductor fabrication and assembly. The proliferation of consumer electronics, smartphones, and AI-enabled devices is fueling demand. Major foundries and OSAT (Outsourced Semiconductor Assembly and Test) providers in the region are scaling up investments in 2.5D/3D packaging and heterogeneous integration to meet global demand (SEMI).

- Rest of World (RoW): While smaller in scale, the RoW segment—including Latin America, the Middle East, and Africa—is gradually adopting stacked die packaging, primarily for telecommunications and emerging industrial applications. Growth is supported by increasing digitalization and government-led technology initiatives, though the region faces challenges related to infrastructure and skilled workforce (Gartner).

Overall, 2025 is expected to see continued regional diversification in stacked die microelectronics packaging, with Asia-Pacific leading in volume, North America and Europe focusing on innovation and strategic autonomy, and RoW regions gradually increasing adoption as digital transformation accelerates globally.

Future Outlook: Emerging Applications and Investment Hotspots

The future outlook for stacked die microelectronics packaging in 2025 is shaped by rapid advancements in semiconductor integration, the proliferation of AI and high-performance computing, and the growing demand for miniaturized, energy-efficient devices. Stacked die packaging, which involves vertically integrating multiple semiconductor dies within a single package, is poised to play a pivotal role in enabling next-generation electronics across several high-growth sectors.

Emerging applications are particularly prominent in data centers, 5G infrastructure, and edge computing. The need for higher bandwidth and lower latency in these environments is driving adoption of 2.5D and 3D stacked die solutions, which offer improved interconnect density and reduced signal loss compared to traditional packaging. For instance, hyperscale data centers are increasingly leveraging high-bandwidth memory (HBM) and logic-on-memory stacking to accelerate AI workloads and big data analytics, a trend highlighted in recent analyses by Gartner and IDC.

Consumer electronics, particularly smartphones and wearables, remain a significant investment hotspot. The push for thinner, lighter devices with enhanced functionality is fueling demand for advanced packaging techniques such as through-silicon via (TSV) and wafer-level stacking. According to Yole Group, the stacked die packaging market in mobile and IoT devices is expected to see double-digit growth through 2025, as OEMs seek to integrate more features without increasing device footprint.

Automotive electronics represent another emerging application area, especially as electric vehicles (EVs) and autonomous driving systems require compact, high-reliability computing modules. Stacked die packaging enables the integration of sensors, processors, and memory in a single module, supporting real-time data processing and advanced driver-assistance systems (ADAS). McKinsey & Company projects that automotive semiconductor content will outpace overall vehicle growth, with stacked die solutions playing a central role.

- Key investment hotspots for 2025 include advanced memory (HBM, 3D NAND), AI accelerators, 5G/6G base stations, and automotive ADAS modules.

- Asia-Pacific, led by Taiwan and South Korea, is expected to dominate manufacturing and R&D investments, as noted by SEMI.

- Strategic partnerships between foundries, OSATs, and system integrators are accelerating innovation and commercialization of stacked die technologies.

In summary, stacked die microelectronics packaging is set to underpin critical advances in computing, connectivity, and mobility in 2025, with robust investment and innovation focused on high-growth, high-value application domains.

Challenges, Risks, and Strategic Opportunities

Stacked die microelectronics packaging, a critical enabler for high-density, high-performance electronic systems, faces a complex landscape of challenges and risks in 2025, but also presents significant strategic opportunities for industry players. The primary technical challenge remains thermal management. As more dies are vertically integrated, heat dissipation becomes increasingly problematic, risking device reliability and performance degradation. Advanced thermal interface materials and innovative heat spreader designs are being explored, but their integration adds cost and complexity to the manufacturing process (SEMI).

Yield and reliability risks are also heightened in stacked die architectures. The increased number of interconnects, such as through-silicon vias (TSVs), raises the probability of defects, impacting overall yield. Furthermore, the mechanical stresses induced during stacking and packaging can lead to die cracking or delamination, especially as package sizes shrink and die counts increase. These reliability concerns necessitate rigorous testing and inspection protocols, which can extend time-to-market and inflate costs (Yole Group).

Supply chain complexity is another significant risk. Stacked die packaging often requires collaboration across multiple vendors for wafer fabrication, die thinning, stacking, and final assembly. Disruptions in any segment—such as shortages of advanced substrates or delays in high-precision bonding equipment—can cascade through the production timeline. The ongoing geopolitical tensions and material shortages observed in recent years have underscored the vulnerability of these intricate supply chains (Gartner).

Despite these challenges, strategic opportunities abound. The surging demand for high-bandwidth memory, AI accelerators, and 5G/6G infrastructure is driving investment in stacked die solutions. Companies that can innovate in areas such as heterogeneous integration, chiplet architectures, and advanced thermal management stand to capture significant market share. Strategic partnerships between foundries, OSATs (Outsourced Semiconductor Assembly and Test), and EDA tool providers are emerging as a key success factor, enabling end-to-end solutions that address both technical and supply chain risks (TSMC).

In summary, while stacked die microelectronics packaging in 2025 is fraught with technical, reliability, and supply chain risks, it also offers substantial growth opportunities for those able to navigate the evolving landscape with innovation and strategic collaboration.

Sources & References

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Semiconductor Industry Association

- IDC

- McKinsey & Company