Отчет по рынку микроэлектронной упаковки с использованием сложенных чипов на 2025 год: рост, технологические изменения и стратегические инсайты на следующие 5 лет. Исследуйте ключевые тренды, прогнозы и конкурентная динамика, формирующая отрасль.

- Резюме и обзор рынка

- Ключевые технологические тренды в микроэлектронной упаковке с использованием сложенных чипов

- Конкурентная среда и ведущие игроки

- Прогнозы роста рынка (2025–2030): CAGR, анализ доходов и объемов

- Региональный анализ рынка: Северная Америка, Европа, Азия-Тихоокеанский регион и остальной мир

- Будущий прогноз: новые приложения и точки инвестирования

- Проблемы, риски и стратегические возможности

- Источники и ссылки

Резюме и обзор рынка

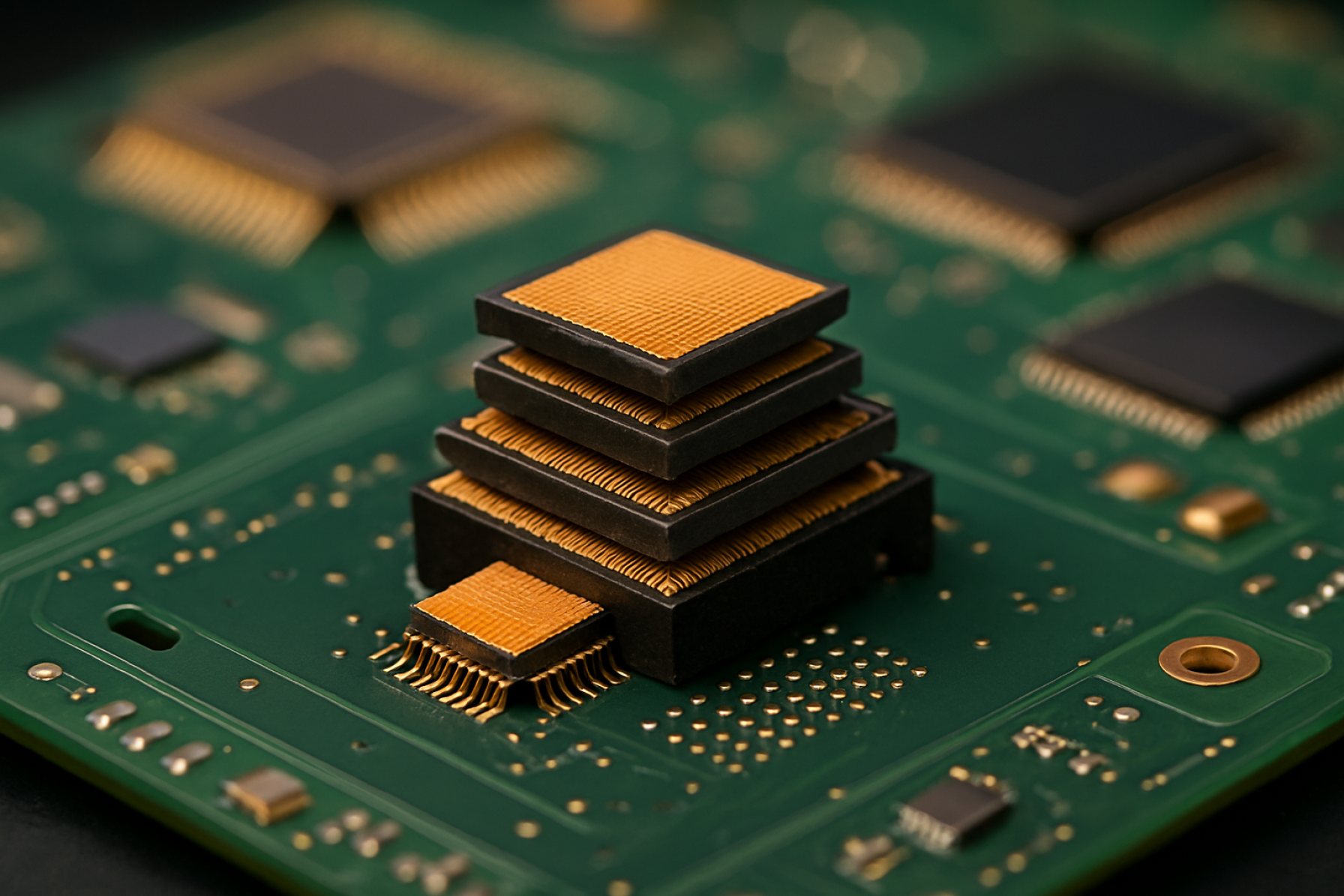

Микроэлектронная упаковка с использованием сложенных чипов предполагает интеграцию нескольких полупроводниковых чипов в одной упаковке, расположенных вертикально для оптимизации пространства, производительности и функциональности. Эта передовая упаковочная технология играет важную роль в удовлетворении растущих требований к миниатюризации, более высокой производительности и энергоэффективности в таких секторах, как потребительская электроника, автомобилестроение, телекоммуникации и центры обработки данных. На 2025 год мировой рынок микроэлектронной упаковки с использованием сложенных чипов демонстрирует устойчивый рост, вызванный распространением устройств 5G, приложений искусственного интеллекта (ИИ) и Интернета вещей (IoT).

Согласно данным Yole Group, рынок передовой упаковки, который включает решения со сложенными чипами, прогнозируется на уровне более 50 миллиардов долларов к 2025 году, при этом архитектуры со сложенными чипами занимают значительную долю благодаря их применению в высококачественных логических, памяти и гетерогенной интеграции. Спрос на память с высокой полосой пропускания (HBM), 3D NAND и решения в упаковке (SiP) ускоряет переход к конфигурациям со сложенными чипами, так как они обеспечивают большую плотность соединений и улучшенную электрическую производительность по сравнению с традиционной 2D упаковкой.

Ключевые игроки отрасли, такие как TSMC, Samsung Electronics и Intel Corporation, активно инвестируют в исследования и разработки для продвижения технологий сквозного кремниевого соединения (TSV) и упаковки на уровне пластин (WLP), которые являются основой для интеграции сложенных чипов. Эти инновации позволяют производить устройства меньшего размера, большей скорости и более энергоэффективные, особенно в вычислениях высокой производительности и мобильных приложениях.

По регионам, Азия-Тихоокеанский регион доминирует на рынке микроэлектронной упаковки с использованием сложенных чипов, возглавляемый производственными центрами на Тайване, в Южной Корее и Китае. Регион получает выгоду от сильной цепочки поставок полупроводников и активных инвестиций в объекты упаковки следующего поколения. Северная Америка и Европа также наблюдают за увеличением принятия, особенно в автомобилях и инфраструктуре центров обработки данных, где решения со сложенными чипами имеют решающее значение для удовлетворения строгих требований к производительности и надежности.

Смотря в будущее к 2025 году, рынок микроэлектронной упаковки с использованием сложенных чипов ожидает сохранения двузначного темпа роста (CAGR), стимулируемого продолжающимися технологическими достижениями и постоянным стремлением к миниатюризации устройств. Тем не менее, такие проблемы, как управление теплом, оптимизация выхода и ограничения цепочки поставок, остаются основными аспектами для участников рынка, стремящихся воспользоваться этим динамичным сегментом.

Ключевые технологические тренды в микроэлектронной упаковке с использованием сложенных чипов

Микроэлектронная упаковка с использованием сложенных чипов находится на переднем крае инноваций в области полупроводников, обеспечивая более высокую производительность устройств, повышенную функциональность и уменьшенные размеры благодаря вертикальной интеграции нескольких полупроводниковых чипов в одну упаковку. По мере продвижения отрасли в 2025 год несколько ключевых технологических трендов формируют эволюцию и принятие решений со сложенными чипами.

- Передовая интеграция сквозного кремниевого соединения (TSV): Технология TSV остается центральной для архитектур со сложенными чипами, обеспечивая высокоплотные вертикальные соединения. Последние достижения сосредоточены на уменьшении диаметра и шага соединений, что улучшает целостность сигнала и энергоэффективность. Ведущие заводы, такие как TSMC и Samsung Electronics, стремятся к масштабированию TSV, чтобы поддерживать память с высокой полосой пропускания (HBM3) и интеграцию логики и памяти для приложений ИИ и высокопроизводительных вычислений (HPC).

- Гетерогенная интеграция: Тенденция к интеграции различных чиплетов — логики, памяти, аналоговых и радиочастотных — в рамках одной сложенной упаковки ускоряется. Этот подход позволяет оптимизировать систему и поддерживает растущий спрос на специализированные интегральные схемы (ASIC) в центрах обработки данных, автомобилях и мобильных устройствах. Технология Intel Foveros и 3D V-Cache от AMD демонстрируют коммерческое принятие гетерогенной укладки.

- Упаковка на уровне пластин (WLP) и технологии выноса: Упаковка на уровне пластин и технологии выноса панелей набирают популярность благодаря своей способности обеспечивать более мелкие шаги соединений и улучшенные тепловые характеристики. ASE Technology Holding и Amkor Technology инвестируют в передовые линии WLP, чтобы удовлетворить спрос на компактные, высокопроизводительные потребительские и автомобильные электроники.

- Инновации в управлении теплом: По мере роста плотности энергии эффективный отвод тепла становится критически важным. Исследуются новые материалы (например, алмазные композиты, продвинутые TIM) и интегрированное микрофлюидное охлаждение для решения тепловых узких мест в упаковках со сложенными чипами, как это подчеркивается в последних рыночных отчетах Yole Group.

- Автоматизация проектирования и решения для тестирования: Сложность архитектур со сложенными чипами способствует принятию передовых инструментов автоматизации проектирования электроники (EDA) и методологий встроенного самотестирования (BIST). Такие компании, как Synopsys и Cadence Design Systems, разрабатывают решения для оптимизации проектирования, проверки и выхода в 3D ИК.

Ожидается, что эти технологические тренды ускорят принятие микроэлектронной упаковки с использованием сложенных чипов в 2025 году, поддерживая новые приложения в областях ИИ, 5G, автомобилестроения и вычислений на границе.

Конкурентная среда и ведущие игроки

Конкурентная среда рынка микроэлектронной упаковки с использованием сложенных чипов в 2025 году характеризуется интенсивными инновациями, стратегическими партнерствами и акцентом на передовых интеграционных технологиях. Упаковка со сложенными чипами, позволяющая вертикальную интеграцию нескольких полупроводниковых чипов в одну упаковку, является критически важным фактором для вычислений высокой производительности, мобильных устройств и новых приложений, таких как искусственный интеллект (ИИ) и 5G связи.

Ведущими игроками на этом рынке являются Тайваньская компания по производству полупроводников (TSMC), Samsung Electronics, Intel Corporation и Amkor Technology. Эти компании зарекомендовали себя как пионеры в области передовых упаковочных решений, используя свой опыт в производстве пластин, 3D интеграции и технологиях систем в упаковке (SiP).

TSMC продолжает лидировать с помощью своих продвинутых платформ 3D упаковки, таких как CoWoS (Chip-on-Wafer-on-Substrate) и SoIC (System on Integrated Chips), которые широко используются для высокопроизводительных вычислений и ускорителей ИИ. Samsung Electronics достигла значительного прогресса с помощью своей технологии X-Cube (eXtended-Cube), позволяющей интеграцию памяти с высокой плотностью и высокой полосой пропускания для мобильных и серверных приложений следующего поколения. Intel продвигает свою технологию 3D укладки Foveros, которая позволяет гетерогенную интеграцию логических и памятьевых чипов, поддерживая стремление компании в области ИИ и рынков центров обработки данных.

Поставщики аутсорсинга сборки и тестирования полупроводников (OSAT), такие как Amkor Technology и ASE Technology Holding, также являются ключевыми игроками, предлагая широкий портфель услуг по упаковке со сложенными чипами для компаний-фабрик и производителей интегральных устройств (IDMs). Эти OSAT инвестируют в передовые линии упаковки и сотрудничают с заводами для ускорения выхода на рынок сложных многочиповых решений.

- TSMC: Лидерство в платформах CoWoS и SoIC для ИИ и HPC.

- Samsung Electronics: Технология X-Cube для интеграции памяти с высокой пропускной способностью.

- Intel Corporation: 3D укладка Foveros для гетерогенной интеграции.

- Amkor Technology и ASE Technology Holding: Продвинутые OSAT услуги для решений со сложенными чипами.

По мере увеличения спроса на миниатюризацию и производительность ожидается дальнейшая консолидация конкурентной среды, при этом ведущие игроки активно инвестируют в НИОКР и партнерства в экосистеме, чтобы поддерживать свои технологические преимущества в микроэлектронной упаковке с использованием сложенных чипов.

Прогнозы роста рынка (2025–2030): CAGR, анализ доходов и объемов

Рынок микроэлектронной упаковки с использованием сложенных чипов готов к устойчивому росту в период с 2025 по 2030 год, вызванному растущим спросом на высокопроизводительные, миниатюризированные электронные устройства в таких секторах, как потребительская электроника, автомобилестроение, телекоммуникации и здравоохранение. Согласно прогнозам MarketsandMarkets, мировой рынок 3D ИК и упаковки со сложенными чипами ожидает зарегистрировать годовой средний темп роста (CAGR) примерно 12–14% в этот период. Эта траектория роста поддерживается растущим принятием передовых упаковочных решений для устранения ограничений традиционных 2D архитектур, особенно в отношении эффективности энергопотребления, форм-фактора и полосы пропускания данных.

Прогнозы по доходам показывают, что рынок микроэлектронной упаковки с использованием сложенных чипов может превысить 15 миллиардов долларов США к 2030 году, по сравнению с оценочными 7,5 миллиарда долларов США в 2025 году. Этот всплеск обусловлен распространением приложений, требующих высокой плотности интеграции, таких как ускорители искусственного интеллекта (ИИ), инфраструктура 5G и устройства edge computing. Ожидается, что регион Азия-Тихоокеанский, возглавляемый такими странами, как Китай, Южная Корея и Тайвань, будет доминировать по доле рынка, занимая более 50% глобальных доходов, благодаря концентрации фабрик и объектов упаковки полупроводников в регионе (Gartner).

По объему ожидается, что число единиц сложенных чипов, отправленных на рынок, будет расти с CAGR 13–15% с 2025 по 2030 год. Это увеличение объема обусловлено быстрой реализацией смартфонов следующего поколения, носимых устройств и электроники для автомобилей, все из которых требуют компактных, высокопроизводительных упаковочных решений. Особенно ожидается, что сектор автомобилестроения увидит самый быстрый рост объема, поскольку электрические автомобили (EV) и системы помощи водителю (ADAS) все больше полагаются на архитектуры со сложенными чипами для повышения вычислительной мощности и надежности (Yole Group).

- CAGR (2025–2030): 12–14%

- Доход (2030): >15 миллиардов долларов США

- CAGR по объему (2025–2030): 13–15%

- Ключевые факторы роста: ИИ, 5G, электроника для автомобилей, миниатюризация

- Ведущий регион: Азия-Тихоокеанский регион

Региональный анализ рынка: Северная Америка, Европа, Азия-Тихоокеанский регион и остальной мир

Глобальный рынок микроэлектронной упаковки с использованием сложенных чипов наблюдает динамичный рост, при этом региональные тренды формируются технологическими достижениями, спросом пользователей и развитием цепочки поставок. В 2025 году рынки Северной Америки, Европы, Азия-Тихоокеанского региона и остального мира (RoW) представляют собой отличительные рыночные характеристики и факторы роста.

- Северная Америка: Североамериканский рынок поддерживается robustними инвестициями в передовое производство полупроводников и сильным присутствием ведущих технологий. Акцент региона на вычисления высокой производительности, инфраструктуру 5G и электронику для автомобилей стимулирует спрос на решения по упаковке со сложенными чипами. Соединенные Штаты, в частности, получают выгоду от инициатив правительства по стимулированию производства чипов на внутреннем рынке, как видно на примере Закона CHIPS, который, как ожидается, ускорит принятие передовых технологий упаковки в 2025 году (Ассоциация полупроводниковой промышленности).

- Европа: Рынок микроэлектронной упаковки с использованием сложенных чипов в Европе характеризуется акцентом на автомобильные, промышленные автоматизации и IoT приложения. Стремление региона к технологическому суверенитету и Европейский Закон о полупроводниках способствуют инвестициям в местные экосистемы полупроводников. Германия и Франция лидируют в НИОКР и пилотном производстве, при этом растет акцент на энергоэффективные и миниатюризированные устройства (Ассоциация производителей электронных компонентов Европы).

- Азия-Тихоокеанский регион: Азия-Тихоокеанский регион остается крупнейшим и самым быстрорастущим рынком для упаковки со сложенными чипами, движимым доминированием стран, таких как Китай, Южная Корея, Тайвань и Япония в области производства и сборки полупроводников. Распространение потребительской электроники, смартфонов и устройств, поддерживающих ИИ, стимулирует спрос. Основные заводы и поставщики OSAT (аутсорсинг сборки и тестирования полупроводников) в регионе увеличивают инвестиции в 2.5D/3D упаковку и гетерогенную интеграцию для удовлетворения глобального спроса (SEMI).

- Остальной мир (RoW): Хотя по масштабам меньше, сегмент RoW — включая Латинскую Америку, Ближний Восток и Африку — постепенно принимает упаковку со сложенными чипами, в основном для телекоммуникаций и новых промышленных приложений. Растущее цифровое развитие и инициативы, возглавляемые правительствами, поддерживают рост, но регион сталкивается с проблемами, связанными с инфраструктурой и квалифицированной рабочей силой (Gartner).

В целом, ожидается, что в 2025 году продолжится региональная диверсификация в микроэлектронной упаковке с использованием сложенных чипов, при этом Азия-Тихоокеанский регион будет лидировать по объемам, Северная Америка и Европа будут сосредотачиваться на инновациях и стратегической автономии, а регионы RoW постепенно увеличат принятие по мере ускорения цифровой трансформации на глобальном уровне.

Будущий прогноз: новые приложения и точки инвестирования

Будущий прогноз для микроэлектронной упаковки с использованием сложенных чипов в 2025 году формируется быстрыми достижениями в интеграции полупроводников, распространением ИИ и высокопроизводительных вычислений, а также растущим спросом на миниатюризированные и энергетически эффективные устройства. Упаковка с использованием сложенных чипов, которая включает вертикальную интеграцию нескольких полупроводниковых чипов в одной упаковке, готова сыграть ключевую роль в обеспечении электроники следующего поколения в нескольких высокоразвивающихся сферах.

Новые приложения особенно ярко проявляются в центрах обработки данных, инфраструктуре 5G и edge computing. Необходимость в более высокой полосе пропускания и меньшей задержке в этих средах стимулирует принятие решений со сложенными чипами 2.5D и 3D, которые предлагают более высокую плотность соединений и уменьшенные потери сигнала по сравнению с традиционной упаковкой. Например, гипермасштабируемые центры обработки данных все чаще используют память с высокой полосой пропускания (HBM) и логику на памяти, чтобы ускорить рабочие нагрузки ИИ и аналитику больших данных, что отражено в последних анализах Gartner и IDC.

Потребительская электроника, особенно смартфоны и носимые устройства, остается значительной точкой инвестирования. Стремление к более тонким и легким устройствам с улучшенной функциональностью стимулирует спрос на передовые упаковочные технологии, такие как сквозное кремниевое соединение (TSV) и упаковка на уровне пластин. Согласно Yole Group, рынок упаковки со сложенными чипами в мобильных и IoT устройствах ожидает двузначного роста до 2025 года, поскольку OEM стремятся интегрировать больше функций без увеличения площади устройства.

Электроника для автомобилей представляет собой еще одну область новых приложений, особенно поскольку электрические автомобили (EV) и системы автономного вождения требуют компактных и надежных вычислительных модулей. Упаковка с использованием сложенных чипов позволяет интегрировать датчики, процессоры и память в одном модуле, поддерживая обработку данных в реальном времени и системы помощи водителю (ADAS). McKinsey & Company прогнозирует, что содержание полупроводников в автомобилях будет превышать общий рост автомобилей, при этом решения со сложенными чипами будут играть центральную роль.

- Ключевые точки инвестирования в 2025 году включают передовые памяти (HBM, 3D NAND), ускорители ИИ, базовые станции 5G/6G и модули ADAS для автомобилей.

- Ожидается, что Азия-Тихоокеанский регион, возглавляемый Тайванем и Южной Кореей, будет доминировать по инвестициям в производство и НИОКР, как отметила SEMI.

- Стратегические партнерства между фабриками, OSAT и системными интеграторами ускоряют инновации и коммерциализацию технологий со сложенными чипами.

В заключение, микроэлектронная упаковка с использованием сложенных чипов готова поддержать критические достижения в вычислениях, связи и мобильности в 2025 году, с активными инвестициями и инновациями, сосредоточенными на высокорастущих и высокоценных приложениях.

Проблемы, риски и стратегические возможности

Микроэлектронная упаковка с использованием сложенных чипов, критически важная для высокоплотных и высокопроизводительных электронных систем, сталкивается с сложным ландшафтом проблем и рисков в 2025 году, но также предлагает значительные стратегические возможности для участников отрасли. Основным техническим вызовом остается управление теплом. По мере вертикальной интеграции большего числа чипов отвод тепла становится все более проблематичным, что ставит под угрозу надежность устройства и его производительность. Исследуются передовые термоинтерфейсные материалы и инновационные конструкции теплоотводов, но их интеграция добавляет стоимость и сложность в производственный процесс (SEMI).

Риски выхода и надежности также увеличиваются в архитектурах со сложенными чипами. Увеличенное число соединений, таких как сквозные кремниевые соединения (TSV), увеличивает вероятность дефектов, что влияет на общий выход. Кроме того, механические напряжения, возникающие во время укладки и упаковки, могут привести к растрескиванию или расслоению чипов, особенно по мере уменьшения размеров упаковки и увеличения числа чипов. Эти проблемы надежности требуют строгих протоколов тестирования и инспекции, что может увеличить время выхода на рынок и повысить затраты (Yole Group).

Сложность цепочки поставок — еще один значительный риск. Упаковка со сложенными чипами часто требует сотрудничества между несколькими поставщиками для изготовления пластин, истончения чипов, укладки и окончательной сборки. Нежелательные события в любом сегменте — такие как нехватка передовых подложек или задержки в оборудовании высокоточной спайки — могут каскадно влиять на производственный цикл. Непрерывные геополитические напряженности и нехватки материалов, наблюдаемые в последние годы, подчеркивают уязвимость этих сложных цепочек поставок (Gartner).

Несмотря на эти вызовы, стратегические возможности обширны. Растущий спрос на память с высокой пропускной способностью, ускорители ИИ и инфраструктура 5G/6G подстегивают инвестиции в решения со сложенными чипами. Компании, которые могут вести инновации в таких областях, как гетерогенная интеграция, архитектуры чиплетов и передовое управление теплом, могут занять значительную долю рынка. Стратегические партнерства между фабриками, OSAT (аутсорсинг сборки и тестирования полупроводников) и поставщиками инструментов EDA становятся ключевым фактором успеха, позволяя предлагать комплексные решения, которые решают как технические, так и цепочные риски поставок (TSMC).

В заключение, несмотря на множество технических, надежностных и цепочных рисков, микроэлектронная упаковка с использованием сложенных чипов в 2025 году представляет собой значительные возможности для роста для тех, кто сможет справиться с изменениями в окружающей среде с помощью инноваций и стратегического сотрудничества.

Источники и ссылки

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Ассоциация полупроводниковой промышленности

- IDC

- McKinsey & Company