Relatório do Mercado de Embalagem de Microeletrônica com Die Empilhado 2025: Crescimento, Mudanças Tecnológicas e Insights Estratégicos para os Próximos 5 Anos. Explore as Principais Tendências, Previsões e Dinâmicas Competitivas que Estão Moldando a Indústria.

- Resumo Executivo & Visão Geral do Mercado

- Principais Tendências Tecnológicas na Embalagem de Microeletrônica com Die Empilhado

- Panorama Competitivo e Principais Players

- Previsões de Crescimento do Mercado (2025–2030): CAGR, Análise de Receita e Volume

- Análise do Mercado Regional: América do Norte, Europa, Ásia-Pacífico e Resto do Mundo

- Perspectivas Futuras: Aplicações Emergentes e Pontos de Investimento

- Desafios, Riscos e Oportunidades Estratégicas

- Fontes & Referências

Resumo Executivo & Visão Geral do Mercado

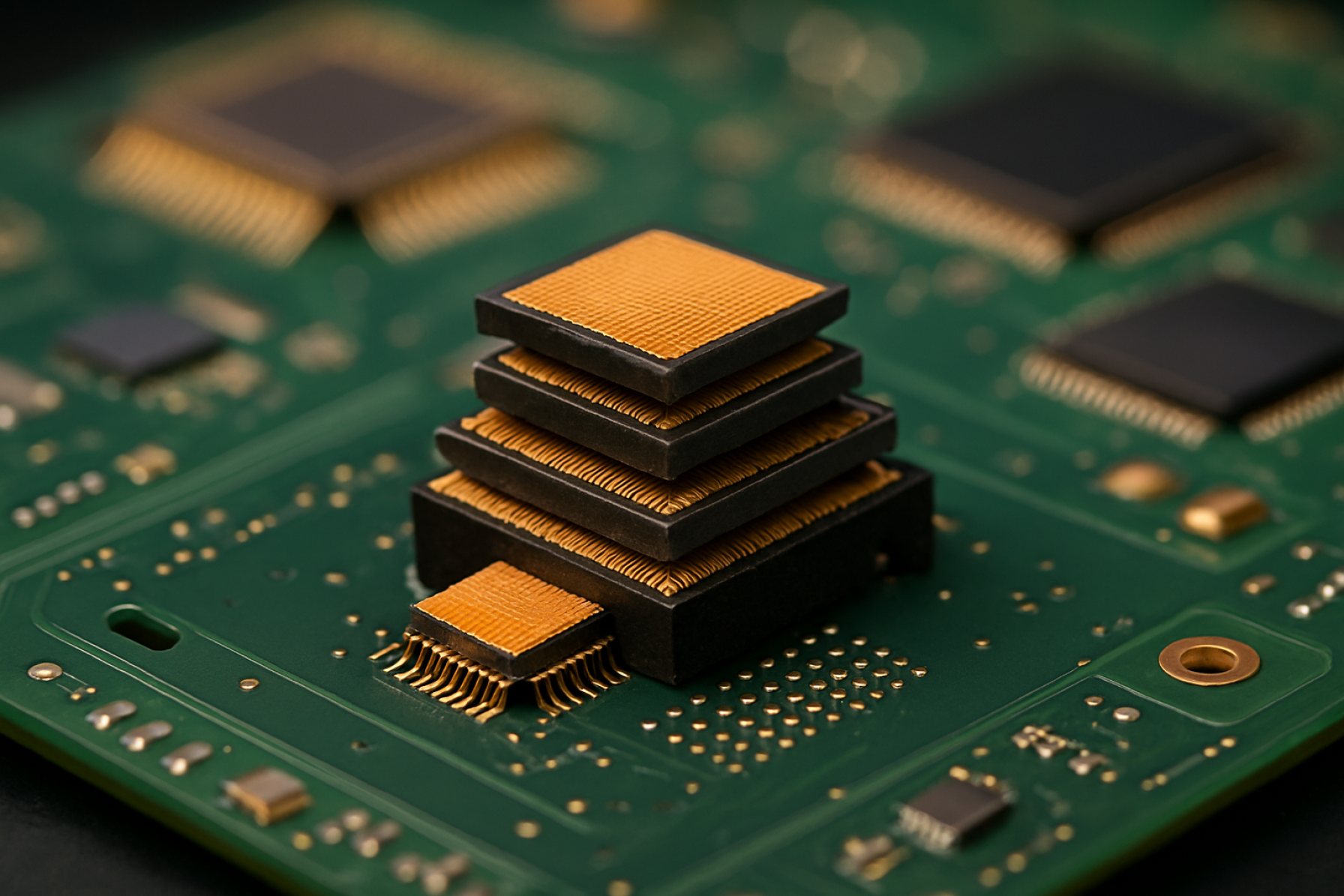

A embalagem de microeletrônica com die empilhado refere-se à integração de múltiplos dies semicondutores dentro de um único pacote, organizados verticalmente para otimizar espaço, desempenho e funcionalidade. Esta tecnologia de embalagem avançada é fundamental para atender à crescente demanda por miniaturização, maior desempenho e eficiência energética em setores como eletrônicos de consumo, automotivo, telecomunicações e centros de dados. Em 2025, o mercado global de embalagem de microeletrônica com die empilhado está experimentando um crescimento robusto, impulsionado pela proliferação de dispositivos 5G, aplicações de inteligência artificial (IA) e a Internet das Coisas (IoT).

Segundo o Yole Group, o mercado de embalagem avançada, que inclui soluções de die empilhado, deve alcançar mais de US$ 50 bilhões até 2025, com arquiteturas de die empilhado representando uma parte significativa devido à sua adoção na lógica de alta gama, memória e integração heterogênea. A demanda por memória de alta largura de banda (HBM), 3D NAND e soluções de sistema-em-pacote (SiP) está acelerando a transição para configurações de die empilhado, já que essas permitem maior densidade de interconexão e melhor desempenho elétrico em comparação com a embalagem 2D tradicional.

Principais players da indústria, como TSMC, Samsung Electronics e Intel Corporation, estão investindo pesadamente em pesquisa e desenvolvimento para avançar nas tecnologias de thru-silicon via (TSV) e embalagem em nível de wafer (WLP), que são fundamentais para a integração de die empilhado. Essas inovações possibilitam a produção de dispositivos menores, mais rápidos e mais eficientes em termos de energia, especialmente em computação de alto desempenho e aplicações móveis.

Regionalmente, a Ásia-Pacífico domina o mercado de embalagem de microeletrônica com die empilhado, liderada por centros de manufatura em Taiwan, Coreia do Sul e China. A região se beneficia de uma forte cadeia de suprimentos de semicondutores e investimentos agressivos em instalações de embalagem de próxima geração. A América do Norte e a Europa também estão testemunhando uma adoção crescente, especialmente na eletrônica automotiva e na infraestrutura de centros de dados, onde soluções de die empilhado são críticas para atender a rigorosas exigências de desempenho e confiabilidade.

Olhando para 2025, espera-se que o mercado de embalagem de microeletrônica com die empilhado mantenha uma taxa de crescimento anual composta (CAGR) de dois dígitos, impulsionado por avanços tecnológicos contínuos e a busca incessante pela miniaturização de dispositivos. No entanto, desafios como gerenciamento térmico, otimização de rendimento e restrições na cadeia de suprimentos continuam sendo pontos focais para os stakeholders da indústria que buscam capitalizar esse dinâmico segmento de mercado.

Principais Tendências Tecnológicas na Embalagem de Microeletrônica com Die Empilhado

A embalagem de microeletrônica com die empilhado está na vanguarda da inovação em semicondutores, permitindo maior desempenho dos dispositivos, funcionalidade aumentada e redução de fatores de forma, ao integrar verticalmente múltiplos dies semicondutores em um único pacote. À medida que a indústria avança para 2025, várias tendências tecnológicas importantes estão moldando a evolução e a adoção de soluções de die empilhado.

- Integração Avançada de Thru-Silicon Via (TSV): A tecnologia TSV permanece central para arquiteturas de die empilhado, fornecendo interconexões verticais de alta densidade. Avanços recentes se concentram em reduzir o diâmetro e o espaçamento dos vias, o que melhora a integridade do sinal e a eficiência energética. Fundições líderes, como TSMC e Samsung Electronics, estão promovendo a escala do TSV para suportar memória de alta largura de banda (HBM3) e integração lógica-memória para aplicações de IA e HPC.

- Integração Heterogênea: A tendência de integrar chiplets diversos—lógica, memória, analógica e RF—em um único pacote empilhado está acelerando. Essa abordagem permite a otimização em nível de sistema e apoia a crescente demanda por circuitos integrados específicos para aplicações (ASICs) em centros de dados, automotivo e dispositivos móveis. Foveros da Intel e 3D V-Cache da AMD exemplificam a adoção comercial do empilhamento heterogêneo.

- Embalagem em Nível de Wafer (WLP) e Tecnologias de Fan-Out: O empilhamento em nível de wafer e a embalagem fan-out em nível de painel estão ganhando destaque pela capacidade de oferecer pitches de interconexão mais finos e desempenho térmico melhorado. ASE Technology Holding e Amkor Technology estão investindo em linhas avançadas de WLP para atender à demanda por eletrônicos de consumo e automotivos compactos e de alto desempenho.

- Inovações em Gerenciamento Térmico: Com o aumento das densidades de potência, a dissipação efetiva de calor torna-se crítica. Novos materiais (por exemplo, compósitos de diamante, TIMs avançados) e resfriamento microfluídico integrado estão sendo explorados para resolver gargalos térmicos em pacotes de die empilhado, como destacado em relatórios de mercado recentes do Yole Group.

- Automação de Design e Soluções de Teste: A complexidade das arquiteturas de die empilhado está impulsionando a adoção de ferramentas avançadas de automação de design eletrônico (EDA) e metodologias de teste automático (BIST). Empresas como Synopsys e Cadence Design Systems estão desenvolvendo soluções para agilizar o design, verificação e otimização de rendimento de ICs 3D.

Essas tendências tecnológicas devem acelerar a adoção de embalagem de microeletrônica com die empilhado em 2025, suportando aplicações de próxima geração em IA, 5G, automotivo e computação em borda.

Panorama Competitivo e Principais Players

O panorama competitivo do mercado de embalagem de microeletrônica com die empilhado em 2025 é caracterizado por intensa inovação, parcerias estratégicas e foco em tecnologias avançadas de integração. A embalagem com die empilhado, que permite a integração vertical de múltiplos dies semicondutores em um único pacote, é um habilitador crítico para computação de alto desempenho, dispositivos móveis e aplicações emergentes, como inteligência artificial (IA) e comunicações 5G.

Os principais players desse mercado incluem a Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation e Amkor Technology. Essas empresas se estabeleceram como pioneiras em soluções de embalagem avançada, aproveitando sua expertise em fabricação de wafers, integração 3D e tecnologias de sistema-em-pacote (SiP).

A TSMC continua a liderar com suas plataformas avançadas de embalagem 3D, como CoWoS (Chip-on-Wafer-on-Substrate) e SoIC (System on Integrated Chips), que são amplamente adotadas para computação de alto desempenho e aceleradores de IA. A Samsung Electronics fez grandes avanços com sua tecnologia X-Cube (eXtended-Cube), que possibilita a integração de memória de alta densidade e alta largura de banda para aplicações móveis e de servidor de próxima geração. A Intel está avançando com sua tecnologia de empilhamento 3D Foveros, que permite a integração heterogênea de dies de lógica e memória, apoiando o impulso da empresa para os mercados de IA e centros de dados.

Fornecedores de montagem e teste de semicondutores terceirizados (OSAT), como Amkor Technology e ASE Technology Holding, também são players-chave, oferecendo um amplo portfólio de serviços de embalagem com die empilhado para empresas de semicondutores fabless e fabricantes de dispositivos integrados (IDMs). Esses OSATs estão investindo em linhas de embalagem avançadas e colaborando com fundições para acelerar o tempo de comercialização de soluções complexas de múltiplos dies.

- TSMC: Liderança nas plataformas CoWoS e SoIC para IA e HPC.

- Samsung Electronics: Tecnologia X-Cube para integração de memória de alta largura de banda.

- Intel Corporation: Empilhamento 3D Foveros para integração heterogênea.

- Amkor Technology e ASE Technology Holding: Serviços OSAT avançados para soluções de die empilhado.

À medida que a demanda por miniaturização e desempenho se intensifica, espera-se que o panorama competitivo veja mais consolidação, com players líderes investindo pesadamente em P&D e parcerias de ecossistema para manter sua vantagem tecnológica na embalagem de microeletrônica com die empilhado.

Previsões de Crescimento do Mercado (2025–2030): CAGR, Análise de Receita e Volume

O mercado de embalagem de microeletrônica com die empilhado está posicionado para um crescimento robusto entre 2025 e 2030, impulsionado pela crescente demanda por dispositivos eletrônicos compactos e de alto desempenho em setores como eletrônicos de consumo, automotivo, telecomunicações e saúde. Segundo projeções do MarketsandMarkets, o mercado global de ICs 3D e embalagem de die empilhado deve registrar uma taxa de crescimento anual composta (CAGR) de aproximadamente 12–14% durante esse período. Essa trajetória de crescimento é sustentada pela adoção crescente de soluções de embalagem avançadas para abordar as limitações das arquiteturas 2D tradicionais, particularmente em termos de eficiência energética, fator de forma e largura de banda de dados.

Previsões de receita indicam que o mercado de embalagem de microeletrônica com die empilhado pode ultrapassar US$ 15 bilhões até 2030, em comparação com cerca de US$ 7,5 bilhões em 2025. Esse aumento é atribuído à proliferação de aplicações que requerem integração de alta densidade, como aceleradores de inteligência artificial (IA), infraestrutura 5G e dispositivos de computação em borda. A região da Ásia-Pacífico, liderada por países como China, Coreia do Sul e Taiwan, deve dominar a participação de mercado, respondendo por mais de 50% das receitas globais, devido à concentração de instalações de fabricação e embalagem de semicondutores na região (Gartner).

Em termos de volume, o número de unidades de die empilhado enviadas deve crescer a uma CAGR de 13–15% de 2025 a 2030. Essa expansão de volume é impulsionada pelo rápido lançamento de smartphones de próxima geração, dispositivos vestíveis e eletrônicos automotivos, todos os quais requerem soluções de embalagem compactas e de alto desempenho. Notavelmente, o setor automotivo deve testemunhar o crescimento de volume mais rápido, à medida que veículos elétricos (EVs) e sistemas avançados de assistência ao condutor (ADAS) dependem cada vez mais de arquiteturas de die empilhado para maior poder computacional e confiabilidade (Yole Group).

- CAGR (2025–2030): 12–14%

- Receita (2030): >US$ 15 bilhões

- CAGR de Volume (2025–2030): 13–15%

- Principais Motores de Crescimento: IA, 5G, eletrônicos automotivos, miniaturização

- Principal Região: Ásia-Pacífico

Análise do Mercado Regional: América do Norte, Europa, Ásia-Pacífico e Resto do Mundo

O mercado global de embalagem de microeletrônica com die empilhado está testemunhando um crescimento dinâmico, com tendências regionais moldadas por avanços tecnológicos, demanda dos usuários finais e desenvolvimentos na cadeia de suprimentos. Em 2025, os mercados da América do Norte, Europa, Ásia-Pacífico e Resto do Mundo (RoW) apresentam características e motores de crescimento distintos.

- América do Norte: O mercado da América do Norte é impulsionado por investimentos robustos em fabricação avançada de semicondutores e uma forte presença de empresas de tecnologia líderes. O foco da região em computação de alto desempenho, infraestrutura 5G e eletrônica automotiva está impulsionando a demanda por soluções de embalagem com die empilhado. Os Estados Unidos, em particular, beneficiam-se de iniciativas governamentais para fortalecer a produção doméstica de chips, como visto na Lei CHIPS, que deve acelerar a adoção de tecnologias avançadas de embalagem em 2025 (Semiconductor Industry Association).

- Europa: O mercado de embalagem de microeletrônica com die empilhado da Europa é caracterizado pelo foco em aplicações automotivas, automação industrial e IoT. O impulso da região por soberania tecnológica e a Lei de Chips da Europa estão promovendo investimentos em ecossistemas locais de semicondutores. Alemanha e França estão liderando em P&D e produção piloto, com uma ênfase crescente em dispositivos miniaturizados e energeticamente eficientes (European Electronic Component Manufacturers Association).

- Ásia-Pacífico: A Ásia-Pacífico continua sendo o maior e mais rápido mercado de embalagem de die empilhado, impulsionado pela dominância de países como China, Coreia do Sul, Taiwan e Japão na fabricação e montagem de semicondutores. A proliferação de eletrônicos de consumo, smartphones e dispositivos habilitados para IA está alimentando a demanda. Grandes fundições e fornecedores de OSAT (Outsourced Semiconductor Assembly and Test) na região estão ampliando os investimentos em embalagem 2.5D/3D e integração heterogênea para atender à demanda global (SEMI).

- Resto do Mundo (RoW): Embora menor em escala, o segmento RoW—incluindo América Latina, Oriente Médio e África—está gradualmente adotando embalagem com die empilhado, principalmente para telecomunicações e aplicações industriais emergentes. O crescimento é apoiado pela crescente digitalização e iniciativas tecnológicas lideradas pelo governo, embora a região enfrente desafios relacionados à infraestrutura e mão de obra qualificada (Gartner).

No geral, 2025 deve ver uma continuidade da diversificação regional na embalagem de microeletrônica com die empilhado, com a Ásia-Pacífico liderando em volume, América do Norte e Europa focando em inovação e autonomia estratégica, e regiões do RoW aumentando gradualmente a adoção à medida que a transformação digital acelera globalmente.

Perspectivas Futuras: Aplicações Emergentes e Pontos de Investimento

As perspectivas futuras para a embalagem de microeletrônica com die empilhado em 2025 são moldadas por avanços rápidos na integração de semicondutores, a proliferação de IA e computação de alto desempenho, e a crescente demanda por dispositivos miniaturizados e energeticamente eficientes. A embalagem com die empilhado, que envolve a integração vertical de múltiplos dies semicondutores em um único pacote, está prestes a desempenhar um papel fundamental na habilitação de eletrônicos de próxima geração em vários setores de alto crescimento.

Aplicações emergentes são particularmente proeminentes em centros de dados, infraestrutura 5G e computação em borda. A necessidade de maior largura de banda e menor latência nesses ambientes está impulsionando a adoção de soluções de die empilhado 2.5D e 3D, que oferecem maior densidade de interconexão e menor perda de sinal em comparação com a embalagem tradicional. Por exemplo, centros de dados hiperescaláveis estão cada vez mais utilizando memória de alta largura de banda (HBM) e empilhamento lógica-sobre-memória para acelerar cargas de trabalho de IA e análise de big data, uma tendência destacada em análises recentes do Gartner e IDC.

Eletrônicos de consumo, especialmente smartphones e dispositivos vestíveis, permanecem um ponto de investimento significativo. A pressão por dispositivos mais finos e leves com funcionalidade aprimorada está alimentando a demanda por técnicas de embalagem avançadas, como thru-silicon via (TSV) e empilhamento em nível de wafer. Segundo o Yole Group, o mercado de embalagem de die empilhado em dispositivos móveis e IoT deve ver um crescimento de dois dígitos até 2025, à medida que os OEMs buscam integrar mais recursos sem aumentar a área do dispositivo.

Eletrônicos automotivos representam outra área de aplicação emergente, especialmente à medida que veículos elétricos (EVs) e sistemas de condução autônoma exigem módulos de computação compactos e de alta confiabilidade. A embalagem com die empilhado permite a integração de sensores, processadores e memória em um único módulo, apoiando processamento de dados em tempo real e sistemas avançados de assistência ao condutor (ADAS). McKinsey & Company projeta que o conteúdo de semicondutores automotivos superará o crescimento geral dos veículos, com soluções de die empilhado desempenhando um papel central.

- Os principais pontos de investimento para 2025 incluem memória avançada (HBM, 3D NAND), aceleradores de IA, estação base 5G/6G e módulos ADAS automotivos.

- A Ásia-Pacífico, liderada por Taiwan e Coreia do Sul, deve dominar investimentos em fabricação e P&D, conforme notado pela SEMI.

- Parcerias estratégicas entre fundições, OSATs e integradores de sistemas estão acelerando a inovação e comercialização de tecnologias de die empilhado.

Em resumo, a embalagem de microeletrônica com die empilhado está pronta para apoiar avanços críticos em computação, conectividade e mobilidade em 2025, com investimentos robustos e inovação focados em domínios de aplicação de alto crescimento e alto valor.

Desafios, Riscos e Oportunidades Estratégicas

A embalagem de microeletrônica com die empilhado, um habilitador crítico para sistemas eletrônicos de alta densidade e alto desempenho, enfrenta um cenário complexo de desafios e riscos em 2025, mas também apresenta oportunidades estratégicas significativas para os players da indústria. O principal desafio técnico permanece sendo o gerenciamento térmico. À medida que mais dies são integrados verticalmente, a dissipação de calor torna-se cada vez mais problemática, colocando em risco a confiabilidade e o desempenho dos dispositivos. Materiais avançados de interface térmica e designs de dissipadores de calor inovadores estão sendo explorados, mas sua integração aumenta o custo e a complexidade do processo de fabricação (SEMI).

Os riscos de rendimento e confiabilidade também são elevados nas arquiteturas de die empilhado. O aumento do número de interconexões, como vias através do silício (TSVs), eleva a probabilidade de defeitos, impactando o rendimento geral. Além disso, as tensões mecânicas induzidas durante o empilhamento e a embalagem podem levar a trincas ou delaminação dos dies, especialmente à medida que os tamanhos dos pacotes diminuem e as contagens de dies aumentam. Essas preocupações com a confiabilidade exigem rigorosos protocolos de teste e inspeção, que podem aumentar o tempo até a comercialização e inflacionar os custos (Yole Group).

A complexidade da cadeia de suprimentos é outro risco significativo. A embalagem com die empilhado muitas vezes requer colaboração entre vários fornecedores para a fabricação de wafers, espessamento de dies, empilhamento e montagem final. Disrupções em qualquer segmento—como escassez de substratos avançados ou atrasos em equipamentos de emparelhamento de alta precisão—podem ter repercussões em toda a linha de produção. As tensões geopolíticas em andamento e as escassezes de materiais observadas nos últimos anos enfatizaram a vulnerabilidade dessas intrincadas cadeias de suprimentos (Gartner).

Apesar desses desafios, oportunidades estratégicas estão se proliferando. A demanda crescente por memória de alta largura de banda, aceleradores de IA e infraestrutura 5G/6G está impulsionando investimentos em soluções de die empilhado. Empresas que puderem inovar em áreas como integração heterogênea, arquiteturas de chiplets e gerenciamento térmico avançado tendem a capturar participação de mercado significativa. Parcerias estratégicas entre fundições, OSATs (Outsourced Semiconductor Assembly and Test) e fornecedores de ferramentas EDA estão emergindo como um fator de sucesso chave, permitindo soluções de ponta a ponta que abordam tanto riscos técnicos quanto da cadeia de suprimentos (TSMC).

Em resumo, embora a embalagem de microeletrônica com die empilhado em 2025 enfrente riscos técnicos, de confiabilidade e da cadeia de suprimentos, também oferece substanciais oportunidades de crescimento para aqueles que conseguirem navegar no cenário em evolução com inovação e colaboração estratégica.

Fontes & Referências

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Semiconductor Industry Association

- IDC

- McKinsey & Company