Raport o rynku pakowania mikroelektroniki z użyciem stakowanych układów scalonych na rok 2025: Wzrost, zmiany technologiczne i strategiczne spostrzeżenia na kolejnych 5 lat. Zbadaj kluczowe trendy, prognozy i dynamiczne uwarunkowania konkurencyjne kształtujące branżę.

- Streszczenie i przegląd rynku

- Kluczowe trendy technologiczne w pakowaniu mikroelektroniki z użyciem stakowanych układów scalonych

- Krajobraz konkurencyjny i wiodący gracze

- Prognozy wzrostu rynku (2025–2030): CAGR, analiza przychodów i wolumenu

- Analiza rynku regionalnego: Ameryka Północna, Europa, Azja-Pacyfik i reszta świata

- Perspektywy na przyszłość: Nowe aplikacje i obszary inwestycyjne

- Wyzwania, ryzyka i strategiczne możliwości

- Źródła i odniesienia

Streszczenie i przegląd rynku

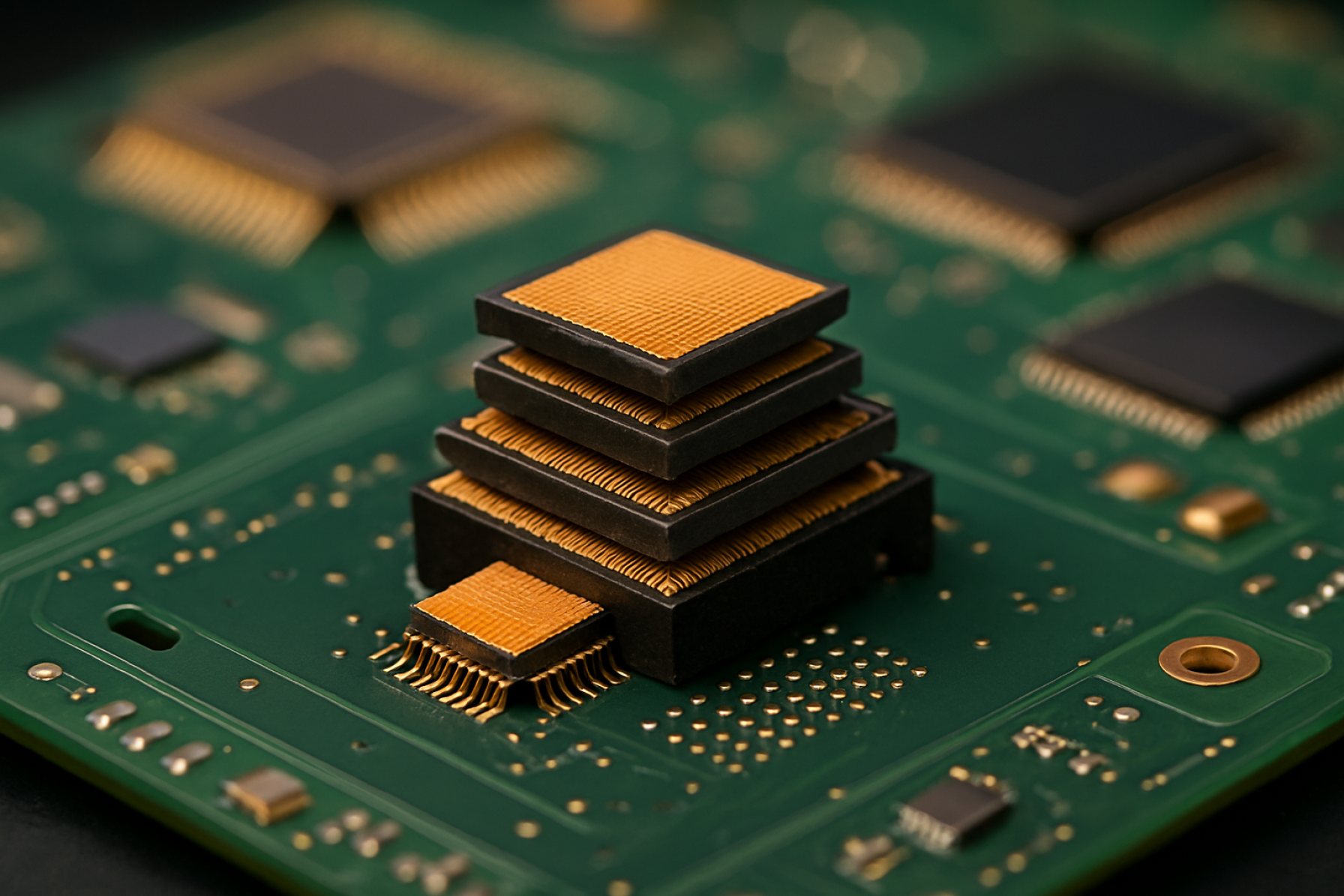

Pakowanie mikroelektroniki z użyciem stakowanych układów scalonych odnosi się do integracji wielu układów scalonych w ramach jednego pakietu, ułożonych pionowo w celu optymalizacji przestrzeni, wydajności i funkcjonalności. Ta zaawansowana technologia pakowania odgrywa kluczową rolę w zaspokajaniu rosnących wymagań dotyczących miniaturyzacji, wyższej wydajności i efektywności energetycznej w sektorach takich jak elektronika użytkowa, motoryzacja, telekomunikacja i centra danych. W 2025 roku globalny rynek pakowania mikroelektroniki z użyciem stakowanych układów scalonych doświadcza dynamicznego wzrostu, napędzanego proliferacją urządzeń 5G, aplikacjami sztucznej inteligencji (AI) oraz Internetem Rzeczy (IoT).

Według Yole Group, rynek zaawansowanego pakowania, który obejmuje rozwiązania stakowanych układów, ma przekroczyć 50 miliardów dolarów do 2025 roku, przy czym architektury stakowanych układów zajmują znaczną część tego rynku dzięki ich zastosowaniu w zaawansowanej logice, pamięci i integracji heterogenicznej. Zapotrzebowanie na pamięć o wysokiej przepustowości (HBM), 3D NAND oraz systemy w pakiecie (SiP) przyspiesza przesunięcie w kierunku konfiguracji stakowanych układów, ponieważ umożliwiają one wyższą gęstość połączeń i lepszą wydajność elektryczną w porównaniu do tradycyjnego pakowania 2D.

Kluczowi gracze branżowi, tacy jak TSMC, Samsung Electronics i Intel Corporation, intensywnie inwestują w badania i rozwój, aby rozwijać technologie vias przezkrystalicznych (TSV) i pakowania na poziomie wafla (WLP), które są fundamentem integracji stakowanych układów. Innowacje te umożliwiają produkcję mniejszych, szybszych i bardziej energooszczędnych urządzeń, szczególnie w komputerach o wysokiej wydajności i aplikacjach mobilnych.

Regionalnie, region Azji-Pacyfiku dominuje na rynku pakowania mikroelektroniki z użyciem stakowanych układów, głównie dzięki centrom produkcyjnym w Tajwanie, Korei Południowej i Chinach. Region korzysta z silnego łańcucha dostaw półprzewodników oraz agresywnych inwestycji w obiekty do pakowania nowej generacji. Ameryka Północna i Europa również obserwują wzrost adopcji, szczególnie w elektronice motoryzacyjnej i infrastrukturze centrów danych, gdzie rozwiązania stakowanych układów są kluczowe dla spełnienia rygorystycznych wymagań dotyczących wydajności i niezawodności.

Patrząc w przyszłość, rynek pakowania mikroelektroniki z użyciem stakowanych układów scalonych ma utrzymać dwu-cyfrową roczną stopę wzrostu (CAGR), napędzaną ciągłymi postępami technologicznymi i nieustannym naciskiem na miniaturyzację urządzeń. Niemniej jednak, wyzwania takie jak zarządzanie ciepłem, optymalizacja wydajności i ograniczenia łańcucha dostaw pozostają kluczowymi kwestiami dla interesariuszy branżowych starających się skorzystać na tym dynamicznym segmencie rynku.

Kluczowe trendy technologiczne w pakowaniu mikroelektroniki z użyciem stakowanych układów scalonych

Pakowanie mikroelektroniki z użyciem stakowanych układów scalonych znajduje się na czołowej linii innowacji w dziedzinie półprzewodników, umożliwiając wyższą wydajność urządzeń, zwiększoną funkcjonalność oraz zmniejszenie rozmiarów dzięki pionowej integracji wielu układów scalonych w ramach jednego pakietu. W miarę, jak branża zbliża się do 2025 roku, kilka kluczowych trendów technologicznych kształtuje rozwój i adoptowanie rozwiązań stakowanych układów.

- Zaawansowana integracja vias przezkrystalicznych (TSV): Technologia TSV pozostaje centralnym elementem architektur stakowanych układów, zapewniając wysokogęste połączenia pionowe. Ostatnie postępy koncentrują się na zmniejszeniu średnicy i rozstawu vias, co zwiększa integralność sygnału i wydajność energetyczną. Wiodące firmy zajmujące się produkcją, takie jak TSMC i Samsung Electronics, posuwają się naprzód w skalowaniu TSV, aby wspierać pamięć o wysokiej przepustowości (HBM3) i integrację logiki z pamięcią w aplikacjach AI i HPC.

- Integracja heterogeniczna: Trend integracji różnorodnych chipletów—logiki, pamięci, analogowych i RF—w ramach jednego stakowanego pakietu przyspiesza. Takie podejście umożliwia optymalizację na poziomie systemu i wspiera rosnące zapotrzebowanie na aplikacyjne układy scalone (ASIC) w centrach danych, motoryzacji i urządzeniach mobilnych. Foveros Intela i 3D V-Cache AMD stanowią przykłady komercyjnej adopcji stakowania heterogenicznego.

- Pakowanie na poziomie wafla (WLP) i technologie fan-out: Stakowanie na poziomie wafla i pakowanie na poziomie paneli fan-out zdobywają na znaczeniu dzięki swojej zdolności do zapewnienia drobniejszych rozstawów połączeń i poprawionej wydajności termicznej. ASE Technology Holding i Amkor Technology inwestują w zaawansowane linie WLP, aby zaspokoić zapotrzebowanie na kompaktowe, wysokowydajne elektroniki użytkowe i motoryzacyjne.

- Innowacje w zarządzaniu ciepłem: W miarę wzrostu gęstości mocy skuteczne odprowadzanie ciepła staje się krytyczne. Badane są nowe materiały (np. kompozyty diamentowe, zaawansowane TIM) oraz zintegrowane chłodzenie mikrofluideczne, aby zająć się wąskimi gardłami cieplnymi w pakietach stakowanych układów, jak wskazują ostatnie raporty rynkowe Yole Group.

- Automatyzacja projektowania i rozwiązania testowe: Złożoność architektur stakowanych układów napędza adopcję zaawansowanych narzędzi automatyzacji projektowania elektronicznego (EDA) oraz metodologii testów wbudowanych (BIST). Firmy takie jak Synopsys i Cadence Design Systems rozwijają rozwiązania mające na celu uproszczenie projektu IC 3D, weryfikacji i optymalizacji wydajności.

Te trendy technologiczne mają przyspieszyć adopcję pakowania mikroelektroniki z użyciem stakowanych układów scalonych w 2025 roku, wspierając aplikacje nowej generacji w AI, 5G, motoryzacji i przetwarzaniu z brzegowym.

Krajobraz konkurencyjny i wiodący gracze

Krajobraz konkurencyjny rynku pakowania mikroelektroniki z użyciem stakowanych układów w 2025 roku charakteryzuje się intensywną innowacyjnością, strategicznymi partnerstwami oraz skupieniem na zaawansowanych technologiach integracji. Pakowanie stakowanych układów, które umożliwia pionową integrację wielu układów scalonych w ramach jednego pakietu, jest kluczowym czynnikiem umożliwiającym wydajną obliczeniowo, mobilne urządzenia oraz nowe aplikacje takie jak sztuczna inteligencja (AI) i komunikacja 5G.

Wiodącymi graczami na tym rynku są Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation oraz Amkor Technology. Firmy te ugruntowały swoją pozycję jako pionierzy w dziedzinie zaawansowanych rozwiązań pakowania, wykorzystując swoją wiedzę w zakresie produkcji wafli, integracji 3D i technologii systemów w pakiecie (SiP).

TSMC nadal prowadzi dzięki swoim zaawansowanym platformom pakowania 3D, takim jak CoWoS (Chip-on-Wafer-on-Substrate) i SoIC (System on Integrated Chips), które są szeroko stosowane w obliczeniach o wysokiej wydajności i przyspieszaczach AI. Samsung Electronics poczynił znaczne postępy dzięki technologii X-Cube (eXtended-Cube), umożliwiając integrację pamięci o wysokiej gęstości i wysokiej przepustowości dla nowej generacji aplikacji mobilnych i serwerowych. Intel rozwija swoją technologię stakowania 3D Foveros, która umożliwia heterogeniczną integrację układów logiki i pamięci, wspierając tym samym wjazd firmy na rynki AI i centrów danych.

Na rynku kluczową rolę odgrywają również dostawcy usług outsourcingowych w zakresie montażu i testowania półprzewodników (OSAT), tacy jak Amkor Technology i ASE Technology Holding, oferując szeroki portfel usług pakowania stakowanych układów dla firm fabless i producentów zintegrowanych. Te OSAT-y inwestują w zaawansowane linie pakowania i współpracują z fabrykami, aby przyspieszyć czas wprowadzenia na rynek skomplikowanych rozwiązań wielodziałowych.

- TSMC: Przywództwo w platformach CoWoS i SoIC dla AI i HPC.

- Samsung Electronics: Technologia X-Cube do integracji pamięci o wysokiej przepustowości.

- Intel Corporation: Stakowanie 3D Foveros do integracji heterogenicznej.

- Amkor Technology i ASE Technology Holding: Zaawansowane usługi OSAT dla rozwiązań stakowanych układów.

W miarę jak rośnie zapotrzebowanie na miniaturyzację i wydajność, krajobraz konkurencyjny prawdopodobnie zobaczy dalszą konsolidację, przy czym wiodący gracze intensywnie inwestują w badania i rozwój oraz partnerstwa ekosystemowe, aby utrzymać swoją przewagę technologiczną w pakowaniu mikroelektroniki z użyciem stakowanych układów.

Prognozy wzrostu rynku (2025–2030): CAGR, analiza przychodów i wolumenu

Rynek pakowania mikroelektroniki z użyciem stakowanych układów jest gotowy na dynamiczny wzrost w latach 2025-2030, napędzany rosnącym zapotrzebowaniem na wysokowydajne, miniaturowe urządzenia elektroniczne w sektorach takich jak elektronika użytkowa, motoryzacja, telekomunikacja i opieka zdrowotna. Według prognoz MarketsandMarkets, globalny rynek 3D IC i pakowania stakowanych układów ma zarejestrować roczną stopę wzrostu na poziomie około 12–14% w tym okresie. Ten tor wzrostu opiera się na coraz większej adopcji zaawansowanych rozwiązań pakowania, które odpowiadają na ograniczenia tradycyjnych architektur 2D, szczególnie pod względem wydajności energetycznej, rozmiaru i przepustowości danych.

Prognozy przychodów wskazują, że rynek pakowania mikroelektroniki z użyciem stakowanych układów może przekroczyć 15 miliardów USD do 2030 roku, w porównaniu z szacowaną kwotą 7,5 miliarda USD w 2025 roku. Ten wzrost jest przypisywany proliferacji aplikacji wymagających wysokiej gęstości integracji, takich jak przyspieszacze AI, infrastruktura 5G i urządzenia do przetwarzania na krawędzi. Region Azji-Pacyfiku, kierowany przez takie kraje jak Chiny, Korea Południowa i Tajwan, ma dominować w udziałach rynkowych, stanowiąc ponad 50% globalnych przychodów, ze względu na koncentrację obiektów produkcyjnych i pakowania półprzewodników w tym regionie (Gartner).

Pod względem wolumenu, liczba jednostek stakowanych układów wychodzących z produkcji ma rosnąć w tempie CAGR wynoszącym 13–15% od 2025 do 2030 roku. Ta ekspansja wolumenu jest napędzana szybkim wprowadzaniem nowych smartfonów, urządzeń noszonych oraz elektroniki motoryzacyjnej, które wszystkie wymagają kompaktowych i wydajnych rozwiązań pakowania. W szczególności sektor motoryzacyjny ma doświadczać najszybszego wzrostu wolumenu, ponieważ pojazdy elektryczne (EV) oraz zaawansowane systemy wspomagania kierowcy (ADAS) coraz bardziej polegają na architekturach stakowanych układów w celu zwiększenia mocy obliczeniowej i niezawodności (Yole Group).

- CAGR (2025–2030): 12–14%

- Przychody (2030): >15 miliardów USD

- CAGR wolumenu (2025–2030): 13–15%

- Kluczowe czynniki wzrostu: AI, 5G, elektronika motoryzacyjna, miniaturyzacja

- Wiodący region: Azja-Pacyfik

Analiza rynku regionalnego: Ameryka Północna, Europa, Azja-Pacyfik i reszta świata

Globalny rynek pakowania mikroelektroniki z użyciem stakowanych układów scalonych doświadcza dynamicznego wzrostu, a trendy regionalne są kształtowane przez zaawansowania technologiczne, popyt ze strony użytkowników końcowych oraz rozwój łańcucha dostaw. W 2025 roku Ameryka Północna, Europa, Azja-Pacyfik i reszta świata (RoW) każdego z tych regionów mają swoje unikalne cechy rynkowe i czynniki wzrostu.

- Ameryka Północna: Rynek Ameryki Północnej jest napędzany solidnymi inwestycjami w zaawansowaną produkcję półprzewodników oraz silną obecnością wiodących firm technologicznych. Skupienie regionu na obliczeniach o wysokiej wydajności, infrastrukturze 5G i elektronice motoryzacyjnej napędza popyt na rozwiązania pakowania stakowanych układów. Stany Zjednoczone, w szczególności, korzystają z inicjatyw rządowych mających na celu wzmocnienie krajowej produkcji chipów, co przejawia się w ustawie CHIPS, która ma przyspieszyć adopcję zaawansowanych technologii pakowania w 2025 roku (Stowarzyszenie Przemysłu Półprzewodnikowego).

- Europa: Europejski rynek pakowania mikroelektroniki z użyciem stakowanych układów cechuje się skupieniem na motoryzacji, automatyzacji przemysłowej i zastosowaniach IoT. Dążenie regionu do suwerenności technologicznej oraz Europejska Ustawa o Chipach wspierają inwestycje w lokalne ekosystemy półprzewodnikowe. Niemcy i Francja prowadzą w badaniach i rozwoju oraz produkcji próbnej, kładąc rosnący nacisk na urządzenia energooszczędne i miniaturowe (Europejskie Stowarzyszenie Producentów Elementów Elektroniki).

- Azja-Pacyfik: Azja-Pacyfik pozostaje największym i najszybciej rozwijającym się rynkiem dla pakowania stakowanych układów, napędzanym dominacją krajów takich jak Chiny, Korea Południowa, Tajwan i Japonia w produkcji i montażu półprzewodników. Proliferacja elektroniki użytkowej, smartfonów i urządzeń z włączoną AI zwiększa popyt. Główne fabryki i dostawcy OSAT (Outsourced Semiconductor Assembly and Test) w regionie zwiększają inwestycje w pakowanie 2.5D/3D i integrację heterogeniczną, aby zaspokoić globalne zapotrzebowanie (SEMI).

- Reszta świata (RoW): Chociaż mniejszy, segment RoW—w tym Ameryka Łacińska, Bliski Wschód i Afryka—stopniowo przyjmuje pakowanie stakowanych układów, głównie w telekomunikacji oraz nowo powstających zastosowaniach przemysłowych. Wzrost jest wspierany przez rosnącą digitalizację i inicjatywy technologiczne prowadzone przez rządy, chociaż region boryka się z wyzwaniami związanymi z infrastrukturą i wykwalifikowaną siłą roboczą (Gartner).

Podsumowując, w 2025 roku można oczekiwać kontynuacji regionalnej dywersyfikacji w pakowaniu mikroelektroniki z użyciem stakowanych układów, przy czym Azja-Pacyfik dominuje pod względem wolumenu, Ameryka Północna i Europa koncentrują się na innowacjach i strategicznej autonomii, a regiony RoW stopniowo zwiększają adopcję, gdy transformacja cyfrowa przyspiesza na całym świecie.

Perspektywy na przyszłość: Nowe aplikacje i obszary inwestycyjne

Perspektywy dla pakowania mikroelektroniki z użyciem stakowanych układów na rok 2025 są kształtowane przez szybki rozwój integracji półprzewodników, proliferację AI i obliczeń o wysokiej wydajności oraz rosnące zapotrzebowanie na miniaturowe, energooszczędne urządzenia. Pakowanie stakowanych układów, które polega na pionowej integracji wielu układów scalonych w jednym pakiecie, ma szansę odegrać kluczową rolę w umożliwieniu elektroniki nowej generacji w wielu sektach o wysokim wzroście.

Nowe aplikacje wyraźnie stają się widoczne w centrach danych, infrastrukturze 5G oraz komputerach na krawędzi. Potrzeba wyższej przepustowości i niższych opóźnień w tych środowiskach napędza adopcję rozwiązań 2.5D i 3D stakowanych układów, które oferują poprawioną gęstość połączeń i zredukowane straty sygnału w porównaniu do tradycyjnych pakowania. Na przykład, hiperskalowe centra danych coraz częściej korzystają z pamięci o wysokiej przepustowości (HBM) oraz stakowania logiki i pamięci, aby przyspieszyć obciążenia AI i analizy dużych danych, co zaakcentowano w niedawnych analizach Gartnera i IDC.

Elektronika użytkowa, szczególnie smartfony i urządzenia noszone, pozostaje istotnym obszarem inwestycyjnym. Dążenie do cieńszych, lżejszych urządzeń o zwiększonej funkcjonalności napędza popyt na zaawansowane techniki pakowania, takie jak vias przezkrystaliczne (TSV) i pakowanie na poziomie wafla. Według Yole Group, rynek pakowania stakowanych układów w urządzeniach mobilnych i IoT ma doświadczyć wzrostu dwucyfrowego do 2025 roku, ponieważ producenci sprzętu oryginalnego (OEM) dążą do integracji większej liczby funkcji bez zwiększenia rozmiaru urządzenia.

Elektronika motoryzacyjna stanowi kolejny obszar nowych aplikacji, szczególnie w miarę postępującego rozwoju pojazdów elektrycznych (EV) i systemów autonomicznego prowadzenia, które wymagają kompaktowych, niezawodnych modułów obliczeniowych. Pakowanie stakowanych układów umożliwia integrację czujników, procesorów i pamięci w jednym module, wspierając przetwarzanie danych w czasie rzeczywistym i zaawansowane systemy wspomagania kierowców (ADAS). McKinsey & Company prognozuje, że zawartość półprzewodnikowa w motoryzacji będzie rosła szybciej niż ogólny wzrost pojazdów, a rozwiązania stakowanych układów odegrają centralną rolę w tym procesie.

- Kluczowe obszary inwestycyjne na rok 2025 obejmują zaawansowaną pamięć (HBM, 3D NAND), przyspieszacze AI, stacje bazowe 5G/6G oraz moduły ADAS w motoryzacji.

- Azja-Pacyfik, kierowana przez Tajwan i Koreę Południową, oczekuje się, że zdominują inwestycje w produkcję i badania i rozwój, jak podaje SEMI.

- Strategiczne partnerstwa między fabrykami, OSAT-ami i integratorami systemów przyspieszają innowacje i komercjalizację technologii stakowanych układów.

Podsumowując, pakowanie mikroelektroniki z użyciem stakowanych układów jest gotowe na wspieranie krytycznych postępów w obliczeniach, łączności i mobilności w 2025 roku, z solidnymi inwestycjami i innowacjami skupionymi na obszarach zastosowań o dużym wzroście i wysokiej wartości.

Wyzwania, ryzyka i strategiczne możliwości

Pakowanie mikroelektroniki z użyciem stakowanych układów, będące kluczowym czynnikiem umożliwiającym wysoką gęstość i wysoką wydajność systemów elektronicznych, napotyka w 2025 roku skomplikowany krajobraz wyzwań i ryzyk, ale także przedstawia znaczące strategiczne możliwości dla graczy branżowych. Głównym technicznym wyzwaniem pozostaje zarządzanie ciepłem. W miarę jak kolejne układy są integrowane pionowo, odprowadzanie ciepła staje się coraz bardziej problematyczne, co zagraża niezawodności urządzenia i degradacji wydajności. Zaawansowane materiały do interfejsów termicznych i innowacyjne projektowanie radiatorów są badane, ale ich integracja zwiększa koszty i złożoność procesu produkcyjnego (SEMI).

Ryzyka związane z wydajnością i niezawodnością są również wyższe w architekturach stakowanych układów. Zwiększona liczba połączeń, takich jak przezkrystaliczne vias (TSV), podnosi prawdopodobieństwo wystąpienia defektów, co wpływa na ogólną wydajność. Co więcej, mechaniczne napięcia wywołane podczas stakowania i pakowania mogą prowadzić do pękania lub delaminacji układów, szczególnie w miarę zmniejszania się rozmiarów pakietów i zwiększania liczby układów. Te obawy dotyczące niezawodności wymagają rygorystycznych protokołów testowania i inspekcji, co może wydłużyć czas wprowadzenia na rynek i zwiększyć koszty (Yole Group).

Złożoność łańcucha dostaw jest kolejnym poważnym ryzykiem. Pakowanie stakowanych układów często wymaga współpracy z wieloma dostawcami w zakresie produkcji wafli, cienkowarstwowych układów scalonych, stakowania i montażu końcowego. Zakłócenia w jakimkolwiek segmencie—takie jak niedobory zaawansowanych substytutów lub opóźnienia w wysokoprecyzyjnym sprzęcie do lutowania—mogą spowodować lawinowe zakłócenia w harmonogramie produkcji. Ongoing geopolitical tensions and material shortages observed in recent years have underscored the vulnerability of these intricate supply chains (Gartner).

Pomimo tych wyzwań istnieje wiele strategicznych możliwości. Rośnie zapotrzebowanie na pamięć o wysokiej przepustowości, przyspieszacze AI oraz infrastrukturę 5G/6G, co napędza inwestycje w rozwiązania stakowanych układów. Firmy, które potrafią innowować w obszarach takich jak integracja heterogeniczna, architektury chipletów oraz zaawansowane zarządzanie ciepłem, mogą zdobyć znaczącą część rynku. Strategic partnership between foundries, OSATs (Outsourced Semiconductor Assembly and Test), and EDA tool providers are emerging as a key success factor, enabling end-to-end solutions that address both technical and supply chain risks (TSMC).

Podsumowując, choć pakowanie mikroelektroniki z użyciem stakowanych układów w 2025 roku jest obarczone ryzykiem technicznym, niezawodnościowym oraz związanym z łańcuchem dostaw, oferuje ono również znaczne możliwości wzrostu dla tych, którzy mogą poruszać się po ewoluującym krajobrazie za pomocą innowacji i strategicznej współpracy.

Źródła i odniesienia

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Stowarzyszenie Przemysłu Półprzewodnikowego

- IDC

- McKinsey & Company