Rapport sur le marché de l’emballage microélectronique à die empilés 2025 : Croissance, changements technologiques et insights stratégiques pour les 5 prochaines années. Explorez les tendances clés, prévisions et dynamiques concurrentielles façonnant l’industrie.

- Résumé Exécutif & Aperçu du Marché

- Tendances Technologiques Clés dans l’Emballage Microélectronique à Die Empilés

- Paysage Concurrentiel et Acteurs Principaux

- Prévisions de Croissance du Marché (2025–2030) : CAGR, Analyse des Revenus et des Volumes

- Analyse du Marché Régional : Amérique du Nord, Europe, Asie-Pacifique et Reste du Monde

- Perspectives Futures : Applications Émergentes et Points Chauds d’Investissement

- Défis, Risques et Opportunités Stratégiques

- Sources & Références

Résumé Exécutif & Aperçu du Marché

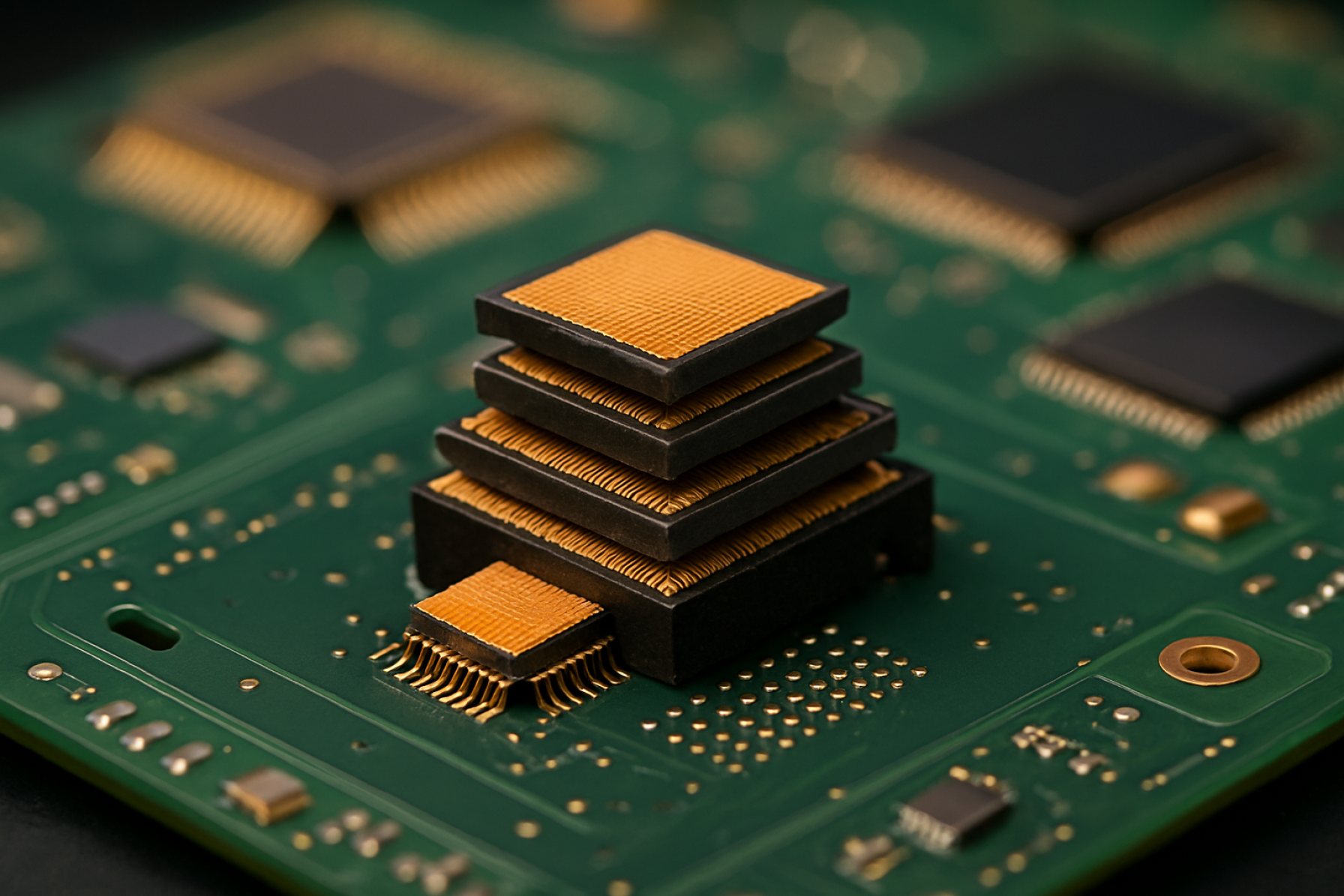

L’emballage microélectronique à die empilés fait référence à l’intégration de plusieurs dies de semi-conducteurs dans un seul emballage, disposés verticalement pour optimiser l’espace, la performance et la fonctionnalité. Cette technologie d’emballage avancée est essentielle pour répondre aux demandes croissantes de miniaturisation, de performances élevées et d’efficacité énergétique dans des secteurs tels que l’électronique grand public, l’automobile, les télécommunications et les centres de données. À partir de 2025, le marché mondial de l’emballage microélectronique à die empilés connaît une forte croissance, impulsée par la prolifération des dispositifs 5G, des applications d’intelligence artificielle (IA) et de l’Internet des objets (IoT).

Selon Yole Group, le marché de l’emballage avancé, qui inclut les solutions à die empilés, devrait dépasser 50 milliards de dollars d’ici 2025, les architectures à die empilés représentant une part significative en raison de leur adoption dans les logiques de haut de gamme, la mémoire et l’intégration hétérogène. La demande pour la mémoire à large bande passante (HBM), la NAND 3D et les solutions de système dans un emballage (SiP) accélère le passage aux configurations à die empilés, car celles-ci permettent une densité d’interconnexion plus élevée et une meilleure performance électrique par rapport à l’emballage 2D traditionnel.

Des acteurs clés de l’industrie tels que TSMC, Samsung Electronics et Intel Corporation investissent massivement dans la recherche et le développement pour faire progresser les technologies de via à travers le silicium (TSV) et d’emballage au niveau des wafers (WLP), qui sont fondamentales pour l’intégration à die empilés. Ces innovations permettent la production de dispositifs plus petits, plus rapides et plus économes en énergie, en particulier dans le calcul haute performance et les applications mobiles.

Régionalement, l’Asie-Pacifique domine le marché de l’emballage microélectronique à die empilés, avec des pôles de fabrication à Taïwan, en Corée du Sud et en Chine. La région bénéficie d’une solide chaîne d’approvisionnement en semi-conducteurs et d’investissements agressifs dans des installations d’emballage de nouvelle génération. L’Amérique du Nord et l’Europe connaissent également une adoption accrue, en particulier dans l’électronique automobile et l’infrastructure des centres de données, où les solutions à die empilés sont essentielles pour répondre aux exigences strictes de performance et de fiabilité.

En regardant vers 2025, le marché de l’emballage microélectronique à die empilés devrait maintenir un taux de croissance annuel composé (CAGR) à deux chiffres, alimenté par des avancées technologiques continues et la poussée incessante pour la miniaturisation des dispositifs. Cependant, des défis tels que la gestion thermique, l’optimisation du rendement et les contraintes de la chaîne d’approvisionnement demeurent des points focaux pour les acteurs de l’industrie cherchant à capitaliser sur ce segment de marché dynamique.

Tendances Technologiques Clés dans l’Emballage Microélectronique à Die Empilés

L’emballage microélectronique à die empilés est à la pointe de l’innovation semi-conductrice, permettant une meilleure performance des dispositifs, une fonctionnalité accrue et des facteurs de forme réduits par l’intégration verticale de plusieurs dies de semi-conducteurs dans un seul emballage. À mesure que l’industrie progresse vers 2025, plusieurs tendances technologiques clés façonnent l’évolution et l’adoption des solutions à die empilés.

- Intégration Avancée de Via à Travers le Silicium (TSV) : La technologie TSV reste centrale pour les architectures à die empilés, fournissant des interconnexions verticales à haute densité. Les avancées récentes se concentrent sur la réduction du diamètre et de l’espacement des vias, ce qui améliore l’intégrité du signal et l’efficacité énergétique. Les fonderies leaders comme TSMC et Samsung Electronics poussent le dimensionnement des TSV pour soutenir la mémoire à large bande passante (HBM3) et l’intégration logique-mémoire pour les applications d’IA et de HPC.

- Intégration Hétérogène : La tendance à intégrer des chiplets divers – logique, mémoire, analogique et RF – dans un seul emballage empilé s’accélère. Cette approche permet une optimisation au niveau du système et répond à la demande croissante pour des circuits intégrés spécifiques à des applications (ASIC) dans les centres de données, l’automobile et les appareils mobiles. Le Foveros d’Intel et le 3D V-Cache d’AMD illustrent l’adoption commerciale du stacking hétérogène.

- Emballage au Niveau des Wafers (WLP) et Technologies Fan-Out : Le stacking au niveau des wafers et l’emballage au niveau des panels Fan-Out gagnent en popularité pour leur capacité à fournir des intervalles d’interconnexion plus fins et de meilleures performances thermiques. ASE Technology Holding et Amkor Technology investissent dans des lignes WLP avancées pour répondre à la demande d’électronique grand public et automobile compactes et performantes.

- Innovations en Gestion Thermique : À mesure que les densités de puissance augmentent, une dissipation de chaleur efficace devient critique. De nouveaux matériaux (par exemple, composites en diamant, TIMs avancés) et des solutions de refroidissement microfluidique intégrées sont explorés pour résoudre les goulets d’étranglement thermiques dans les emballages à die empilés, comme souligné dans les rapports de marché récents du Yole Group.

- Solutions d’Automatisation de Conception et de Test : La complexité des architectures à die empilés pousse à l’adoption d’outils avancés d’automatisation de la conception électronique (EDA) et de méthodologies de test auto-intégré (BIST). Des entreprises comme Synopsys et Cadence Design Systems développent des solutions pour rationaliser la conception, la vérification et l’optimisation du rendement des circuits intégrés 3D.

Ces tendances technologiques devraient accélérer l’adoption de l’emballage microélectronique à die empilés en 2025, soutenant les applications de nouvelle génération dans l’IA, la 5G, l’automobile et l’informatique en périphérie.

Paysage Concurrentiel et Acteurs Principaux

Le paysage concurrentiel du marché de l’emballage microélectronique à die empilés en 2025 est caractérisé par une innovation intense, des partenariats stratégiques et un accent sur les technologies avancées d’intégration. L’emballage à die empilés, qui permet l’intégration verticale de plusieurs dies de semi-conducteurs dans un seul emballage, est un élément clé pour le calcul haute performance, les dispositifs mobiles et des applications émergentes telles que l’intelligence artificielle (IA) et les communications 5G.

Les principaux acteurs de ce marché incluent Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation et Amkor Technology. Ces entreprises se sont imposées comme des pionnières dans les solutions d’emballage avancé, tirant parti de leur expertise en fabrication de wafers, intégration 3D et technologies de système dans un emballage (SiP).

TSMC continue de mener avec ses plates-formes d’emballage 3D avancées, telles que CoWoS (Chip-on-Wafer-on-Substrate) et SoIC (System on Integrated Chips), qui sont largement adoptées pour le calcul haute performance et les accélérateurs IA. Samsung Electronics a réalisé des progrès significatifs avec sa technologie X-Cube (eXtended-Cube), permettant l’intégration de mémoire à haute densité et à large bande passante pour des applications mobiles et serveurs de nouvelle génération. Intel progresse avec sa technologie d’empilage 3D Foveros, permettant l’intégration hétérogène des dies logiques et de mémoire, soutenant la poussée de l’entreprise dans les marchés de l’IA et des centres de données.

Les fournisseurs d’assemblage et de test de semi-conducteurs sous-traités (OSAT) comme Amkor Technology et ASE Technology Holding sont également des acteurs clés, offrant un large éventail de services d’emballage à die empilés aux entreprises de semi-conducteurs sans usine et aux fabricants de dispositifs intégrés (IDM). Ces OSAT investissent dans des lignes d’emballage avancées et collaborent avec des fonderies pour accélérer le délai de mise sur le marché des solutions multi-die complexes.

- TSMC : Leadership dans les plates-formes CoWoS et SoIC pour l’IA et le HPC.

- Samsung Electronics : Technologie X-Cube pour l’intégration de mémoire à large bande passante.

- Intel Corporation : Empilage 3D Foveros pour l’intégration hétérogène.

- Amkor Technology et ASE Technology Holding : Services avancés OSAT pour les solutions à die empilés.

Alors que la demande pour la miniaturisation et la performance s’intensifie, le paysage concurrentiel devrait connaître une consolidation supplémentaire, avec des acteurs de premier plan investissant massivement dans la R&D et des partenariats écosystémiques pour maintenir leur avance technologique dans l’emballage microélectronique à die empilés.

Prévisions de Croissance du Marché (2025–2030) : CAGR, Analyse des Revenus et des Volumes

Le marché de l’emballage microélectronique à die empilés est prêt pour une croissance robuste entre 2025 et 2030, alimentée par une demande croissante pour des dispositifs électroniques miniaturisés et performants dans des secteurs tels que l’électronique grand public, l’automobile, les télécommunications et la santé. Selon les projections de MarketsandMarkets, le marché mondial des circuits intégrés 3D et de l’emballage à die empilés devrait enregistrer un taux de croissance annuel composé (CAGR) d’environ 12–14% pendant cette période. Cette trajectoire de croissance repose sur l’adoption accrue de solutions d’emballage avancées pour surmonter les limitations des architectures 2D traditionnelles, en particulier en matière d’efficacité énergétique, de facteur de forme et de bande passante de données.

Les prévisions de revenus indiquent que le marché de l’emballage microélectronique à die empilés pourrait dépasser 15 milliards USD d’ici 2030, contre environ 7,5 milliards USD en 2025. Cette augmentation est attribuée à la prolifération des applications nécessitant une intégration à haute densité, telles que les accélérateurs d’intelligence artificielle (IA), l’infrastructure 5G et les dispositifs d’informatique en périphérie. La région Asie-Pacifique, menée par des pays comme la Chine, la Corée du Sud et Taïwan, devrait dominer la part du marché, représentant plus de 50% des revenus mondiaux, en raison de la concentration des installations de fabrication et d’emballage de semi-conducteurs dans la région (Gartner).

En termes de volume, le nombre d’unités de die empilés expédiées devrait croître à un CAGR de 13–15% de 2025 à 2030. Cette expansion de volume est soutenue par le déploiement rapide de smartphones de nouvelle génération, d’appareils portables et d’électronique automobile, qui nécessitent tous des solutions d’emballage compactes et performantes. Notamment, le secteur automobile devrait connaître la croissance la plus rapide en volume, alors que les véhicules électriques (EV) et les systèmes avancés d’assistance à la conduite (ADAS) s’appuient de plus en plus sur des architectures à die empilés pour une puissance de calcul et une fiabilité accrues (Yole Group).

- CAGR (2025–2030) : 12–14%

- Revenus (2030) : >15 milliards USD

- CAGR en volume (2025–2030) : 13–15%

- Principaux moteurs de croissance : IA, 5G, électronique automobile, miniaturisation

- Région leader : Asie-Pacifique

Analyse du Marché Régional : Amérique du Nord, Europe, Asie-Pacifique et Reste du Monde

Le marché mondial de l’emballage microélectronique à die empilés connaît une croissance dynamique, avec des tendances régionales façonnées par les avancées technologiques, la demande des utilisateurs finaux et les développements de la chaîne d’approvisionnement. En 2025, chacun des marchés Amérique du Nord, Europe, Asie-Pacifique et Reste du Monde (RoW) présente des caractéristiques et des moteurs de croissance distincts.

- Amérique du Nord : Le marché nord-américain est propulsé par des investissements solides dans la fabrication avancée de semi-conducteurs et une forte présence d’entreprises technologiques de premier plan. L’accent mis par la région sur le calcul haute performance, l’infrastructure 5G et l’électronique automobile stimule la demande pour les solutions d’emballage à die empilés. Les États-Unis, en particulier, bénéficient d’initiatives gouvernementales visant à renforcer la production de puces domestiques, comme le montre la loi CHIPS, qui devrait accélérer l’adoption des technologies d’emballage avancées en 2025 (Semiconductor Industry Association).

- Europe : Le marché européen de l’emballage microélectronique à die empilés se caractérise par un accent sur les applications automobiles, l’automatisation industrielle et l’IoT. L’orientation de la région vers la souveraineté technologique et la loi européenne sur les puces favorisent les investissements dans les écosystèmes de semi-conducteurs locaux. L’Allemagne et la France sont en tête en matière de R&D et de production pilote, avec un accent croissant sur les dispositifs énergétiquement efficaces et miniaturisés (European Electronic Component Manufacturers Association).

- Asie-Pacifique : L’Asie-Pacifique reste le plus grand et le plus rapide marché pour l’emballage à die empilés, tiré par la domination de pays comme la Chine, la Corée du Sud, Taïwan et le Japon dans la fabrication et l’assemblage de semi-conducteurs. La prolifération des appareils électroniques grand public, des smartphones et des dispositifs dotés d’IA alimente la demande. Les grandes fonderies et les fournisseurs OSAT (Outsourced Semiconductor Assembly and Test) de la région augmentent leurs investissements dans l’emballage 2.5D/3D et l’intégration hétérogène pour répondre à la demande mondiale (SEMI).

- Reste du Monde (RoW) : Bien que de plus petite taille, le segment RoW – comprenant l’Amérique latine, le Moyen-Orient et l’Afrique – adopte progressivement l’emballage à die empilés, principalement pour les télécommunications et les applications industrielles émergentes. La croissance est soutenue par l’augmentation de numérique et les initiatives technologiques menées par les gouvernements, bien que la région soit confrontée à des défis liés à l’infrastructure et à la main-d’œuvre qualifiée (Gartner).

Dans l’ensemble, 2025 devrait voir une diversification régionale continue dans l’emballage microélectronique à die empilés, l’Asie-Pacifique menant en volume, l’Amérique du Nord et l’Europe se concentrant sur l’innovation et l’autonomie stratégique, et les régions RoW augmentant progressivement leur adoption à mesure que la transformation numérique s’accélère à l’échelle mondiale.

Perspectives Futures : Applications Émergentes et Points Chauds d’Investissement

Les perspectives futures pour l’emballage microélectronique à die empilés en 2025 sont façonnées par des avancées rapides dans l’intégration des semi-conducteurs, la prolifération de l’IA et du calcul haute performance, ainsi que la demande croissante de dispositifs miniaturisés et écoénergétiques. L’emballage à die empilés, qui consiste à intégrer verticalement plusieurs dies de semi-conducteurs dans un seul emballage, est prêt à jouer un rôle clé dans l’activation des électroniques de prochaine génération dans plusieurs secteurs à forte croissance.

Les applications émergentes sont particulièrement marquées dans les centres de données, l’infrastructure 5G et l’informatique en périphérie. Le besoin d’une bande passante plus élevée et d’une latence plus faible dans ces environnements stimule l’adoption de solutions à die empilés 2.5D et 3D, qui offrent une densité d’interconnexion améliorée et une perte de signal réduite par rapport à l’emballage traditionnel. Par exemple, les centres de données hyperscale s’appuient de plus en plus sur la mémoire à large bande passante (HBM) et l’empilage logique-sur-mémoire pour accélérer les charges de travail d’IA et l’analyse des grandes données, une tendance soulignée dans les analyses récentes par Gartner et IDC.

L’électronique grand public, en particulier les smartphones et les appareils portables, reste un point chaud d’investissement significatif. La poussée vers des dispositifs plus fins et plus légers avec des fonctionnalités améliorées stimule la demande pour des techniques d’emballage avancées telles que les vias à travers le silicium (TSV) et le stacking au niveau des wafers. Selon Yole Group, le marché de l’emballage à die empilés dans les appareils mobiles et IoT devrait connaître une croissance à deux chiffres jusqu’en 2025, alors que les OEMs cherchent à intégrer davantage de fonctionnalités sans augmenter la taille des dispositifs.

L’électronique automobile représente un autre domaine d’application émergent, surtout que les véhicules électriques (EV) et les systèmes de conduite autonome nécessitent des modules de calcul compacts et fiables. L’emballage à die empilés permet l’intégration de capteurs, de processeurs et de mémoire dans un seul module, soutenant le traitement de données en temps réel et les systèmes avancés d’assistance à la conduite (ADAS). McKinsey & Company prévoit que le contenu semi-conducteur automobile dépassera la croissance globale des véhicules, les solutions à die empilés jouant un rôle central.

- Les principaux points chauds d’investissement pour 2025 incluent la mémoire avancée (HBM, NAND 3D), les accélérateurs IA, les stations de base 5G/6G et les modules ADAS automobiles.

- L’Asie-Pacifique, menée par Taïwan et la Corée du Sud, devrait dominer la fabrication et les investissements en R&D, comme l’a noté SEMI.

- Les partenariats stratégiques entre fonderies, OSAT et intégrateurs de systèmes accélèrent l’innovation et la commercialisation des technologies à die empilés.

En résumé, l’emballage microélectronique à die empilés est sur le point de soutenir des avancées critiques en matière de calcul, de connectivité et de mobilité en 2025, avec des investissements et des innovations robustes centrées sur des domaines d’application à forte croissance et à forte valeur ajoutée.

Défis, Risques et Opportunités Stratégiques

L’emballage microélectronique à die empilés, un élément essentiel pour des systèmes électroniques denses et haute performance, fait face à un paysage complexe de défis et de risques en 2025, mais présente également de significatives opportunités stratégiques pour les acteurs de l’industrie. Le principal défi technique demeure la gestion thermique. À mesure que davantage de dies sont intégrés verticalement, la dissipation de chaleur devient de plus en plus problématique, risquant la fiabilité et la dégradation de la performance des dispositifs. Des matériaux avancés d’interface thermique et des conceptions innovantes de dissipateurs de chaleur sont explorés, mais leur intégration ajoute coût et complexité au processus de fabrication (SEMI).

Les risques de rendement et de fiabilité sont également accrus dans les architectures à die empilés. Le nombre accru d’interconnexions, comme les vias à travers le silicium (TSV), augmente la probabilité de défauts, impactant le rendement global. De plus, les contraintes mécaniques induites lors de l’empilage et de l’emballage peuvent entraîner des fissures ou des délaminages de die, surtout à mesure que les tailles des emballages diminuent et que le nombre de dies augmente. Ces préoccupations en matière de fiabilité nécessitent des protocoles de test et d’inspection rigoureux, ce qui peut prolonger le délai de mise sur le marché et augmenter les coûts (Yole Group).

La complexité de la chaîne d’approvisionnement représente un autre risque significatif. L’emballage à die empilés nécessite souvent une collaboration entre plusieurs fournisseurs pour la fabrication des wafers, l’amincissement des dies, l’empilage et l’assemblage final. Des perturbations dans tout segment — des pénuries de substrats avancés ou des retards dans l’équipement de liaison de haute précision — peuvent avoir des répercussions sur le calendrier de production. Les tensions géopolitiques et les pénuries de matériaux observées ces dernières années ont mis en évidence la vulnérabilité de ces chaînes d’approvisionnement complexes (Gartner).

Malgré ces défis, des opportunités stratégiques abondent. La demande croissante pour la mémoire à large bande passante, les accélérateurs IA et l’infrastructure 5G/6G stimule les investissements dans les solutions à die empilés. Les entreprises qui peuvent innover dans des domaines tels que l’intégration hétérogène, les architectures de chiplets et la gestion thermique avancée sont susceptibles de capturer une part de marché significative. Les partenariats stratégiques entre fonderies, OSAT (Outsourced Semiconductor Assembly and Test) et fournisseurs d’outils EDA émergent comme un facteur clé de succès, permettant des solutions de bout en bout qui traitent à la fois des risques techniques et de chaîne d’approvisionnement (TSMC).

En résumé, bien que l’emballage microélectronique à die empilés en 2025 soit rempli de risques techniques, de fiabilité et de chaîne d’approvisionnement, il offre également d’importantes opportunités de croissance pour ceux qui peuvent naviguer dans ce paysage en évolution avec innovation et collaboration stratégique.

Sources & Références

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Semiconductor Industry Association

- IDC

- McKinsey & Company