2025 Stacked Die Mikroelektroniikkapaketoinnin Markkinaraportti: Kasvu, Teknologiset Muutokset ja Strategiset Näkemykset Viidelle Vuodelle. Tutki Tärkeitä Trendejä, Ennusteita ja Kilpailudynamiikkaa, Jotka Muovaavat Teollisuutta.

- Yhteenveto ja Markkinan Yleiskuva

- Keskeiset Teknologiset Trendit Stacked Die Mikroelektroniikkapaketoinnissa

- Kilpailutilanne ja Johtavat Toimijat

- Markkinakasvun Ennusteet (2025–2030): CAGR, Liikevaihto ja Volyymianalyysi

- Alueellinen Markkina-analyysi: Pohjois-Amerikka, Eurooppa, Aasia-Tyahti ja Muut Maailmat

- Tulevaisuuden Näkymät: Uudet Sovellukset ja Investointikeskukset

- Haasteet, Riskit ja Strategiset Mahdollisuudet

- Lähteet ja Viittaukset

Yhteenveto ja Markkinan Yleiskuva

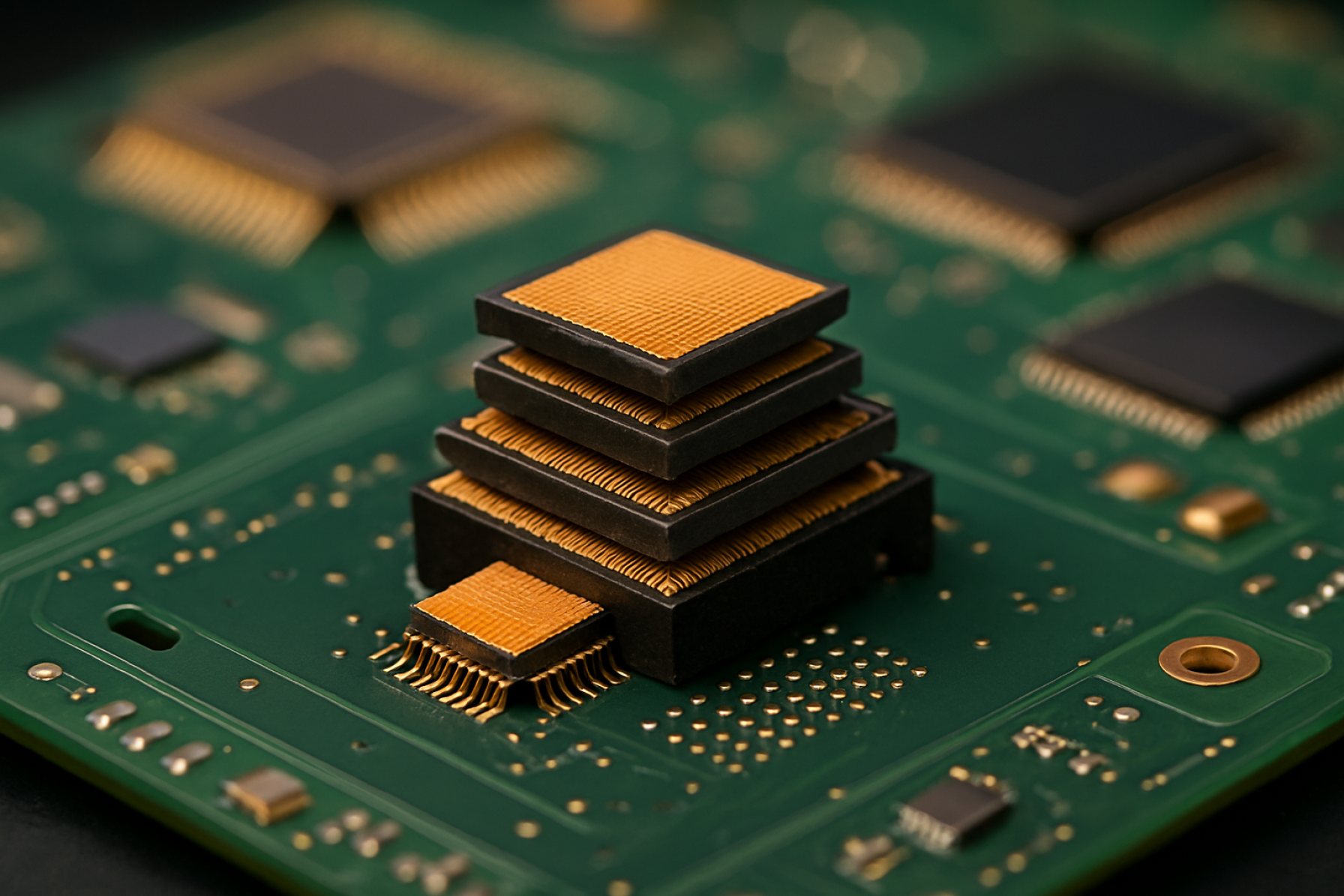

Stacked die mikroelektroniikkapaketointi viittaa useiden puolijohdekranojen integroimiseen yhteen pakkaukseen, joka on järjestetty pystysuoraan tilan, suorituskyvyn ja toiminnallisuuden optimoimiseksi. Tämä edistynyt pakkausteknologia on keskeinen vastattaessa kasvaviin vaatimuksiin miniaturisaatiosta, korkeammasta suorituskyvystä ja energiatehokkuudesta aloilla kuten kulutuselektroniikka, autoilu, tietoliikenne ja datakeskukset. Vuoteen 2025 mennessä globaali stacked die mikroelektroniikkapaketoinnin markkina elää voimakasta kasvua, jota ohjaavat 5G-laitteiden, tekoäly (AI) sovellusten ja esineiden internetin (IoT) lisääntyminen.

Yole Groupin mukaan edistynyt pakkausmarkkina, johon sisältyvät stacked die -ratkaisut, tulee kasvamaan yli 50 miljardiin dollariin vuoteen 2025 mennessä, ja stacked die -arkkitehtuurit muodostavat merkittävän osan, johtuen niiden käytöstä huipputeknologiassa, muistikorteissa ja heterogeenisessä integraatiossa. Korkean kaistanleveyden muistin (HBM), 3D NANDin ja system-in-package (SiP) -ratkaisujen kysyntä nopeuttaa siirtymistä stacked die -kokoonpanoihin, koska ne mahdollistavat korkeamman liitäntätiheyden ja parannettua sähköistä suorituskykyä verrattuna perinteiseen 2D-pakkaamiseen.

Keskeiset toimijat kuten TSMC, Samsung Electronics ja Intel Corporation investoivat voimakkaasti tutkimukseen ja kehitykseen edistääkseen läpivientisilikonia (TSV) ja wafer-tason pakkausteknologioita (WLP), jotka ovat perustana stacked die -integraatiolle. Nämä innovaatiot mahdollistavat pienempien, nopeampien ja energiatehokkaampien laitteiden valmistuksen, erityisesti huipputeknologian laskennassa ja mobiilisovelluksissa.

Alueellisesti Aasia-Tyhä hallitsee stacked die mikroelektroniikkapaketoinnin markkinoita, johon vaikuttavat erityisesti valmistushubina Taiwan, Etelä-Korea ja Kiina. Alue hyötyy vahvasta puolijohdehuollosta ja voimakkaista investoinneista seuraavan sukupolven pakkauslaitoksiin. Pohjois-Amerikka ja Eurooppa näkevät myös lisääntyvää käyttöönottoa, erityisesti autoteollisuuden elektroniikassa ja datakeskusten infrastruktuurissa, joissa stacked die -ratkaisut ovat kriittisiä tiukkojen suorituskyky- ja luotettavuusvaatimusten täyttämisessä.

Katsoen eteenpäin vuoteen 2025 stacked die mikroelektroniikkapaketoinnin markkinoiden odotetaan säilyttävän kaksinumeroinen vuosittainen kasvuprosentti (CAGR), jota tukevat jatkuvat teknologiset kehitykset ja laitteiden miniaturisaation loputon pyrkimys. Kuitenkin haasteet, kuten lämpöhallinta, tuottavuuden optimointi ja toimitusketjun rajoitukset, pysyvät keskiössä teollisuuden sidosryhmille, jotka pyrkivät hyödyntämään tätä dynaamista markkinasegmenttiä.

Keskeiset Teknologiset Trendit Stacked Die Mikroelektroniikkapaketoinnissa

Stacked die mikroelektroniikkapaketointi on puolijohdeinnovaation eturintamassa, mahdollistaen korkeamman laitteen suorituskyvyn, lisääntyneen toiminnallisuuden ja pienemmät muototekijät integroimalla useita puolijohdekranoja yhteen pakettiin pystysuoraan. Kun teollisuus etenee vuoteen 2025, useat keskeiset teknologiset trendit muovaavat stacked die -ratkaisujen kehitystä ja käyttöönottoa.

- Edistynyt Läpivientisilikoni (TSV) Integraatio: TSV-teknologia pysyy keskeisenä stacked die -arkkitehtuureissa, tarjoten tiheät pystysuuntaiset liitännät. Viimeisimmät edistysaskeleet keskittyvät läpiviennin halkaisijan ja välin vähentämiseen, mikä parantaa signaalin eheyttä ja tehotehokkuutta. Johtavat valmistajat kuten TSMC ja Samsung Electronics sysäävät TSV:n mittakaavaa tukemaan korkean kaistanleveyden muistia (HBM3) ja logiikka-muisti-integraatiota AI- ja HPC-sovelluksille.

- Heterogeeninen Integraatio: Suuntaus erilaisiin siruihin—logiikka, muisti, analogi ja RF—integraatiossa yhteen stacked pakettiin kasvaa. Tämä lähestymistapa mahdollistaa järjestelmätason optimoinnin ja tukee kasvavaa kysyntää erityissovelluksiin suunnattuja integroituja piirejä (ASIC) datakeskuksissa, autotekniikassa ja mobiililaitteissa. Intelin Foveros ja AMD:n 3D V-Cache ovat esimerkkejä kaupallisista heterogeenisen pinomisen käyttöönotoista.

- Wafer-tason Pakkaus (WLP) ja Fan-Out Tekniikat: Wafer-tason pinominen ja fan-out paneelitasopakkaus ovat saavuttamassa suosiota kyvykkyyksistään tarjota hienompia liitäntävälejä ja parannettua lämpösuorituskykyä. ASE Technology Holding ja Amkor Technology investoivat edistyneisiin WLP-linjoihin vastatakseen kysyntään kompakteille, huipputeknologian kulutuselektroniikalle ja autoteollisuudelle.

- Lämpöhallinnan Innovaatioita: Kun tehotiheydet kasvavat, tehokas lämpöjohtavuus tulee kriittiseksi. Uusia materiaaleja (esim. timanttikoostumukset, edistyneet TIM:t) ja integroitua mikrofluidista jäähdytystä tutkitaan lämpöpullonkaulojen ratkaisemiseksi stacked die -paketeissa, kuten tuoreissa Yole Groupin markkinaraporteissa on korostettu.

- Suunnitteluautomaatio ja Testausratkaisut: Stacked die -arkkitehtuurien monimutkaisuus vauhdittaa kehittyneiden elektronisten suunnittelun automaatio (EDA) työkalujen ja sisäänrakennettujen itse-testaus (BIST) menetelmien käyttöönottoa. Yritykset kuten Synopsys ja Cadence Design Systems kehittävät ratkaisuja virtaviivaistaakseen 3D IC -suunnittelua, verifiointia ja tuottavuuden optimointia.

Nämä teknologiset trendit odotetaan vauhdittavan stacked die mikroelektroniikkapaketoinnin käyttöönottoa vuonna 2025, tukien seuraavan sukupolven sovelluksia AI:ssa, 5G:ssä, autoilussa ja reunalaskennassa.

Kilpailutilanne ja Johtavat Toimijat

Stacked die mikroelektroniikkapaketoinnin markkinan kilpailutilanne vuonna 2025 on voimakkaasti innovaatioiden, strategisten kumppanuuksien ja edistyneiden integraatioteknologioiden ympärillä. Stacked die -pakkaus, joka mahdollistaa useiden puolijohdekranojen pystysuoran integroinnin yhteen pakettiin, on kriittinen mahdollistaja huipputeknologian laskennalle, mobiililaitteille ja uusille sovelluksille kuten tekoälylle (AI) ja 5G-viestinnälle.

Markkinan johtavat toimijat ovat Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation ja Amkor Technology. Nämä yritykset ovat vakiinnuttaneet asemansa edistyneiden pakkausratkaisujen pioneereina, hyödyntäen asiantuntemustaan waferin valmistuksessa, 3D-integroidussa ja system-in-package (SiP) -tekniikoissa.

TSMC jatkaa johtajuutensa säilyttämistä edistyneillä 3D-pakkausalustoillaan, kuten CoWoS (Chip-on-Wafer-on-Substrate) ja SoIC (System on Integrated Chips), joita käytetään laajalti huipputeknologian laskennassa ja AI-kiihdyttimissä. Samsung Electronics on saavuttanut merkittävää edistystä X-Cube (eXtended-Cube) -teknologiansa kanssa, joka mahdollistaa korkean tiheyden, korkean kaistanleveyden muisti-integraation seuraavan sukupolven mobiili- ja palvelinsovelluksille. Intel kehittää Foveros 3D -pinontateknologiaansa, joka mahdollistaa logiikan ja muistin kranojen heterogeenisen integroinnin, tukien yrityksen edistymistä AI- ja datakeskusten markkinoilla.

Ulkoistetut puolijohdekokoonpanon ja testauksen (OSAT) tarjoajat, kuten Amkor Technology ja ASE Technology Holding, ovat myös avainpelaajia, jotka tarjoavat laajan valikoiman stacked die -pakkauspalveluja piiriä ilman valmistajia (fabless) ja integroiduille laitevalmistajille (IDM). Nämä OSATit investoivat edistyneisiin pakkauslinjoihin ja tekevät yhteistyötä valmistajien kanssa nopeuttaakseen monimutkaisten multi-die-ratkaisujen markkinoille pääsyä.

- TSMC: Johtajuus CoWoS- ja SoIC-alustoilla AI:lle ja HPC:lle.

- Samsung Electronics: X-Cube-teknologia korkean kaistanleveyden muisti-integraatiolle.

- Intel Corporation: Foveros 3D -pinonta heterogeeniselle integraatiolle.

- Amkor Technology ja ASE Technology Holding: Edistyneet OSAT-palvelut stacked die -ratkaisuissa.

Kun miniaturisaation ja suorituskyvyn kysyntä kasvaa, kilpailutilanteen odotetaan näkevän lisäkonsolidointia, jolloin johtavat toimijat investoivat voimakkaasti tutkimukseen ja kehitykseen sekä ekosysteemikumppanuuksiin säilyttääkseen teknologisen etulyöntiasemansa stacked die mikroelektroniikkapaketoinnissa.

Markkinakasvun Ennusteet (2025–2030): CAGR, Liikevaihto ja Volyymianalyysi

Stacked die mikroelektroniikkapaketoinnin markkina on valmiina voimakkaaseen kasvuun vuosina 2025–2030, jota ohjaa kasvava kysyntä huipputeknologian, miniaturisoitujen elektroniikkalaitteiden puolesta useilla aloilla, kuten kulutuselektroniikassa, autoteollisuudessa, tietoliikenteessä ja terveydessä. Ennusteiden mukaan MarketsandMarkets globaali 3D IC ja stacked die pakkausmarkkina tulee rekisteröimään noin 12–14% vuosittaisen kasvuprosentin (CAGR) tänä aikana. Tämä kasvupyrkimys on perustana kehittyvien pakkausratkaisujen lisääntyvälle käyttöönottamiselle perinteisten 2D-arkkitehtuurien rajoitusten, erityisesti tehotehokkuuden, muototekijän ja datakaistanleveyden osalta.

Liikevaihtoennusteet viittaavat siihen, että stacked die mikroelektroniikkapaketoinnin markkina voi ylittää 15 miljardia Yhdysvaltain dollaria vuoteen 2030 mennessä, kun se nousee arvioidusta 7,5 miljardista Yhdysvaltain dollarista vuonna 2025. Tämä kasvu johtuu sovellusten lisääntymisestä, jotka vaativat korkeatiheistä integraatiota, kuten tekoälykiihdyttimiä, 5G-infrastruktuuria ja reunalaskentayksiköitä. Aasia-Tyhä, johon kuuluvat maat kuten Kiina, Etelä-Korea ja Taiwan, odotetaan dominoivan markkinaosuutta, jonka osuus on yli 50% globaalista liikevaihdosta, johtuen alueen puolijohdeteollisuuden ja pakkauslaitosten keskittymisestä (Gartner).

Volyymitasolla toimitettujen stacked die -yksikköjen määrän odotetaan kasvavan CAGR:llä 13–15% vuosina 2025–2030. Tämä volyymi kasvu on vauhdittamassa seuraavan sukupolven älypuhelimien, wearables-laitteiden ja autoteollisuuden elektroniikan nopeaa käyttöönottoa, kaikki tarvitsevat kompakteja, huipputeknologian pakkausratkaisuja. Erityisesti autoteollisuuden odotetaan kokevan nopeinta volyymin kasvua, kun sähköautot (EV) ja kehittyneet kuljettajaa avustavat järjestelmät (ADAS) luottavat yhä enemmän stacked die -kokoonpanoihin parannetun laskennallisen tehon ja luotettavuuden saavuttamiseksi (Yole Group).

- CAGR (2025–2030): 12–14%

- Liikevaihto (2030): >15 miljardia Yhdysvaltain dollaria

- Volyymi CAGR (2025–2030): 13–15%

- Keskeiset Kasvupohjakäytävät: AI, 5G, autoteollisuuden elektroniikka, miniaturisaatio

- Johtava Alue: Aasia-Tyhä

Alueellinen Markkina-analyysi: Pohjois-Amerikka, Eurooppa, Aasia-Tyhä ja Muut Maailmat

Globaali stacked die mikroelektroniikkapaketoinnin markkina kokee dynaamista kasvua, ja alueelliset trendit muovautuvat teknologisten edistysaskelten, loppukäyttäjäkysynnän ja toimitusketjun kehitysten muodossa. Vuonna 2025 Pohjois-Amerikassa, Euroopassa, Aasia-Tyhässä ja Muilla Maailmoilla (RoW) on kunkin merkityksellisiä markkinatuotteita ja kasvupohjia.

- Pohjois-Amerikka: Pohjois-Amerikan markkinat ovat voimakkaasti investoimassa edistyneeseen puolijohdevalmistukseen ja alueen vahvaan teknologiayritysten läsnäoloon. Alueen keskittyminen huipputeknologian laskentaan, 5G-infrastruktuuriin ja autoteollisuuden elektroniikkaan vauhdittaa kysyntää stacked die -pakkausratkaisuille. Yhdysvallat, erityisesti, hyötyy hallituksen aloitteista vahvistaa kotimaista piirikapasiteettia, kuten CHIPS-lainsäädännössä, joka odottaa nopeuttavan edistyneiden pakkausteknologioiden käyttöä vuonna 2025 (Puolijohdeteollisuuden Liitto).

- Eurooppa: Euroopan stacked die mikroelektroniikkapaketoinnin markkina on luonteenomaista keskittymisessään autoteollisuuteen, teolliseen automaatioon ja IoT-sovelluksiin. Alueen teknologisen itsemääräämisoikeuden ja Euroopan Chips Actin pyrkimys edistää investointeja paikallisiin puolijohdeekosysteemeihin. Saksa ja Ranska johtavat tutkimus- ja kehitystoiminnassa ja pilotoinnissa, korostaen yhä enemmän energiatehokkaita ja miniaturisoituja laitteita (Euroopan Elektronikomponenttivalmistajien Liitto).

- Aasia-Tyhä: Aasia-Tyhä pysyy suurimpana ja nopeimmin kasvavana markkinana stacked die -pakkaamiselle, ohjaavana alueella maanjohtavien puolijohteiden valmistuksen ja kokoonpanon hajautumisella. Kulutuselektroniikan, älypuhelimien ja AI-ominaisuuksien lisääntyminen kiihdyttää kysyntää. Suurimmat valmistajat ja OSAT (ulkoa tilattuja puolijohdekokoonpano- ja testaus) tarjoajat alueella skaalautuvat investoimaan 2.5D/3D-pakkaukseen ja heterogeeniseen integraatioon, joka vastaa globaaliin kysyntään (SEMI).

- Muilla Maailmoilla (RoW): Vaikka pienemmässä mittakaavassa, RoW-sektori—mikä kattaa Latinalaisen Amerikan, Lähi-idän ja Afrikan—on vähitellen ottamassa käyttöön stacked die -pakkaamista, ensisijaisesti tietoliikenne- ja kehittyvissä teollisissa sovelluksissa. Kasvu on tukemassa lisääntyvän digitalisaation ja hallituksen vetämän teknologiainitiatiivin kautta, vaikka alue kohtaa haasteita, jotka liittyvät infrastruktuuriin ja osaavaan työvoimaan (Gartner).

Yhteenvetona, vuosi 2025 tulee todennäköisesti näkemään jatkuvaa alueellista diversifikaatiota stacked die mikroelektroniikkapaketoinnissa, Aasia-Tyhä johdonmukaisesti sääntelemässä volyymia, Pohjois-Amerikka ja Eurooppa keskittyen innovaatioksi ja strategiseen autonomiaan, ja RoW-alueet vähitellen lisää siinä käyttöönottamisessa globaalin digitalisaation nopeuttamiseksi.

Tulevaisuuden Näkymät: Uudet Sovellukset ja Investointikeskukset

Tulevaisuuden näkymät stacked die mikroelektroniikkapaketoinnissa vuonna 2025 ovat muotoutuneet puolijohdeeintegraation nopeasta kehityksestä, AI:n ja huipputeknologian laskennan leviämisestä, sekä kasvavasta kysynnästä miniaturisoitujen, energiatehokkaiden laitteiden puolesta. Stacked die pakkaaminen, joka sisältää useiden puolijohdekranojen pystysuoran integroinnin yhteen pakettiin, on asema kriittisessä roolissa seuraavan sukupolven elektroniikassa useilla korkeakasvualueilla.

Uudenlaiset sovellukset ovat erityiset tiedotuksessa datakeskuksissa, 5G-infrastruktuurissa ja reunalaskennassa. Kysyntä korkean kaistanleveyden ja matalan viiveen saavuttamiseksi näissä ympäristöissä vastaavat 2.5D ja 3D stacked die -ratkaisujen käyttöönottoa, mikä tarjoaa parannettua liitäntätiheyttä ja vähentynyttä signaalihäviötä verrattuna perinteisiin pakkausratkaisuihin. Esimerkiksi hypermittaka datakeskukset hyödyntävät yhä enemmän korkean kaistanleveyden muistia (HBM) ja logiikkaa muistiin pinottuna nopeuttaakseen AI-kuormia ja suurta datan analysointia, minkä Gartnerin ja IDC:n äskettäiset analyysit ovat korostaneet.

Kulutuselektroniikka, erityisesti älypuhelimet ja wearables-laitteet, pysyvät merkittävänä investointikeskuksena. Ponnistelu ohjata ohuempia, kevyempiä laitteita, joilla on parannettu toiminnallisuus, sytyttää enemmän vaatimusta edistyneille pakkaustekniikoille, kuten läpivientisilikonia (TSV) ja wafer-tason pinontaa. Yole Groupin mukaan stacked die pakkausmarkkinat mobiili- ja IoT-laitteissa odotetaan saavuttavan kaksinumeroisen kasvun vuoteen 2025 mennessä, koska OEM:t pyrkivät integroimaan enemmän ominaisuuksia ilman, että laitteiden jalanjälkiä laajennetaan.

Autoteollisuuden elektroniikka on toinen nouseva sovellusalue, varsinkin kun sähköautot (EV) ja itsenäiset ajojärjestelmät vaativat kompakteja, korkealaatuisia laskentamoduuleja. Stacked die -pakkaus mahdollistaa antureiden, prosessorien ja muistien integroinnin yhteen moduuliin, tukemalla reaaliaikaista tietojenkäsittelyä ja kehittyneitä kuljettajaa avustavia järjestelmiä (ADAS). McKinsey & Company ennustaa, että autosiemenmateriaalit ohittavat yleisen ajoneuvokasvun, stacked die ratkaisujen ollessa keskeisessä roolissa.

- Tärkeitä investointikeskuksia vuodelle 2025 ovat edistyneet muistipaketit (HBM, 3D NAND), AI-kiihdyttimet, 5G/6G tukiasemat ja autoteollisuuden ADAS-moduulit.

- Aasia-Tyhä, johdonmukaisesti Taiwan ja Etelä-Korea, odottaa hallitsevansa valmistus- ja R&D-investointeja, kuten SEMI on huomannut.

- Strategiset kumppanuudet valmistajien, OSAT-toimijoiden ja järjestelmäintegraattoreiden välillä nopeuttavat stacked die -teknologioiden innovaatiota ja kaupallistamista.

Yhteenvetona, stacked die mikroelektroniikkapaketointi tulee olemaan kriittinen kehitysaskel laskennan, yhteyksien ja liikkuvuuden kehitykselle vuonna 2025, voimakkaalla investoinnilla ja innovaatiolla, keskittyen korkean kasvun ja korkean arvon sovellusalueisiin.

Haasteet, Riskit ja Strategiset Mahdollisuudet

Stacked die mikroelektroniikkapaketointi, joka on kriittinen mahdollistaja korkeatiheille, korkealaatuisille sähköisille järjestelmille, kohtaa vuonna 2025 monimutkaisen haasteiden ja riskien maaston, mutta se tarjoaa myös merkittäviä strategisia mahdollisuuksia teollisuuden toimijoille. Pääasiallinen tekninen haaste on edelleen lämpöhallinta. Kun useampi die pinotaan pystysuoraan, lämpöjohtavuus tulee yhä ongelmallisemmaksi, uhaten laitteiden luotettavuutta ja suorituskyvyn heikkenemistä. Edistyneet lämpöhallintamateriaalit ja innovatiiviset lämpölevittimet ovat tutkittavana, mutta niiden integrointi lisää kustannuksia ja monimutkaisuutta tuotantoprosessiin (SEMI).

Tuottavuuden ja luotettavuuden riskit ovat myös nostettu stacked die -arkkitehtuurissa. Lisääntyneet liitäntämahdollisuudet, kuten läpivientisilikonit (TSV), lisäävät virheiden todennäköisyyttä, mikä vaikuttaa kokonaiskilpailukykyyn. Lisäksi mekaanjiset rasitukset pinonnan ja pakkaamisen aikana voivat johtaa jätteiden rikkoutumiseen tai delaminaatioon, erityisesti kun pakkauskoot pienenevät ja die-määrät kasvavat. Nämä luotettavuusongelmat edellyttävät tiukkoja testaus- ja tarkastusprotokollia, mikä voi pidentää markkinoille pääsyä ja nostaa kustannuksia (Yole Group).

Toimitusketjun monimutkaisuus on toinen merkittävä riski. Stacked die -pakkaaminen vaatii usein yhteistyötä useiden toimittajien kanssa waferin valmistuksessa, die-hionassa, pinonnassa ja lopullisessa kokoonpanossa. Häiriöt missä tahansa segmentissä – kuten edistyneiden substraatien puute tai viivästykset tarkkuusliimauksen laitteistoissa – voivat vaikuttaa tuotantosuunnitelmaan. Viime vuosina havaittu geopolitiikan jännitys ja materiaalipula ovat korostaneet näiden monimutkaisten toimitusketjujen haavoittavuutta (Gartner).

Huolimatta näistä haasteista, strategiset mahdollisuudet ovat runsaita. Korkean kaistanleveyden tietojenkäsittelyn, AI-kiihdyttimien ja 5G/6G-infrastruktuurin kasvanut kysyntä ohjaa investointeja stacked die -ratkaisuihin. Yritykset, jotka voivat innovoida alueilla kuten heterogeeninen integraatio, chiplet-arkkitehtuurit ja edistynyt lämpöhallinta, voivat saavuttaa merkittävän markkinaosuuden. Strategiset kumppanuudet valmistajien, OSAT-toimijoiden ja EDA-työkalujen tarjoajien välillä ovat nousemassa avaintekijäksi onnistumisessa, mahdollistamalla kattavia ratkaisuja, jotka käsittelevät sekä teknisiä että toimitusketjun riskejä (TSMC).

Yhteenvetona, vaikka stacked die mikroelektroniikkapaketointi vuonna 2025 on täynnä teknisiä, luotettavuuteen ja toimitusketjun riskejä, se tarjoaa myös huomattavia kasvumahdollisuuksia niille, jotka pystyvät navigoimaan kehittyvässä maisemassa innovaation ja strategisen yhteistyön avulla.

Lähteet ja Viittaukset

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Puolijohdeteollisuuden Liitto

- IDC

- McKinsey & Company