Informe del Mercado de Embalaje de Microelectrónica de Chip Apilados 2025: Crecimiento, Cambios Tecnológicos y Perspectivas Estratégicas para los Próximos 5 Años. Explora las Principales Tendencias, Pronósticos y Dinámicas Competitivas que Modelan la Industria.

- Resumen Ejecutivo y Visión General del Mercado

- Tendencias Tecnológicas Clave en el Embalaje de Microelectrónica de Chip Apilados

- Panorama Competitivo y Principales Actores

- Pronósticos de Crecimiento del Mercado (2025–2030): CAGR, Análisis de Ingresos y Volumen

- Análisis del Mercado Regional: Norteamérica, Europa, Asia-Pacífico y Resto del Mundo

- Perspectivas Futuras: Aplicaciones Emergentes y Puntos de Inversión Clave

- Desafíos, Riesgos y Oportunidades Estratégicas

- Fuentes y Referencias

Resumen Ejecutivo y Visión General del Mercado

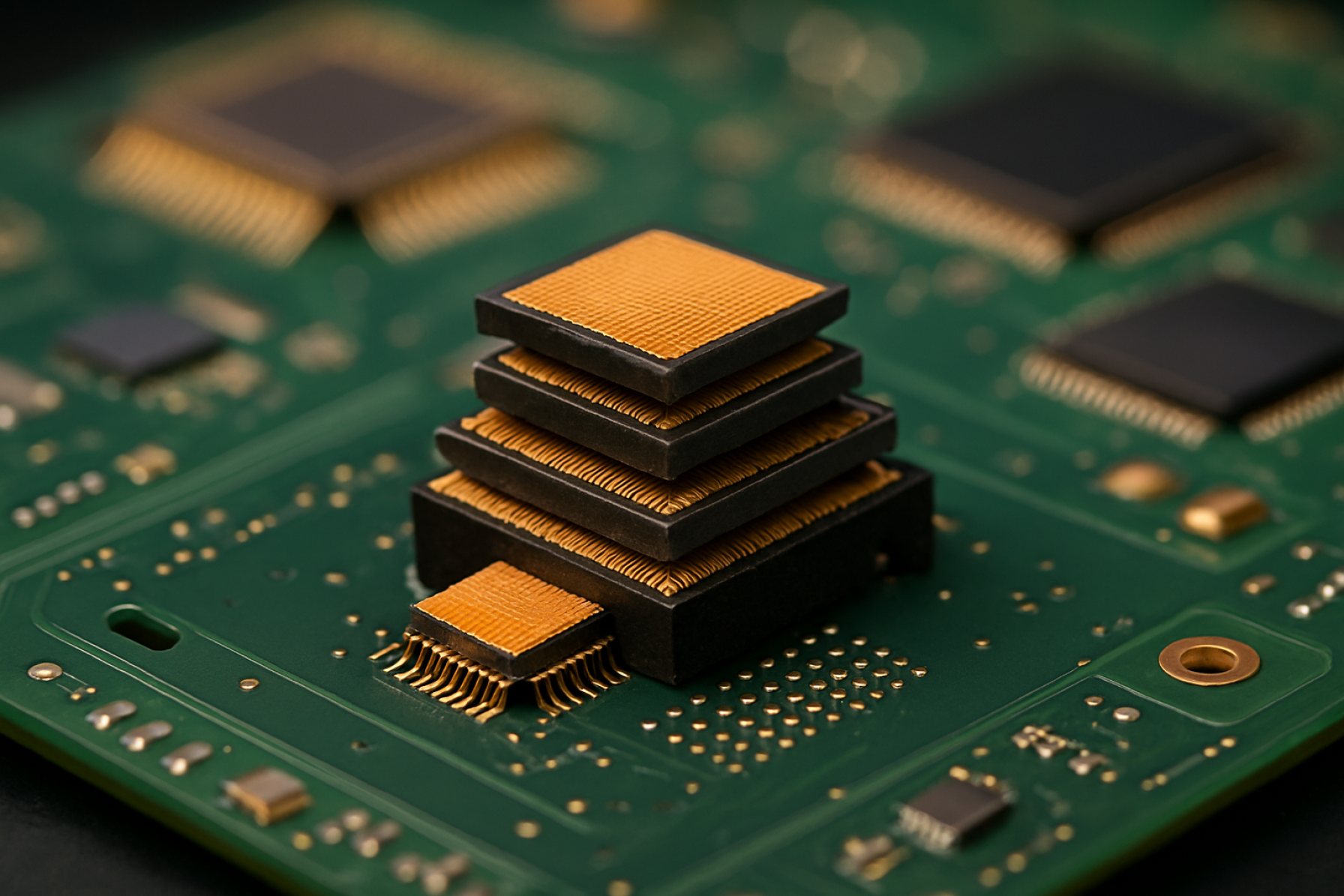

El embalaje de microelectrónica de chip apilados se refiere a la integración de múltiples chips semiconductores dentro de un solo paquete, organizados verticalmente para optimizar espacio, rendimiento y funcionalidad. Esta avanzada tecnología de embalaje es fundamental para satisfacer las crecientes demandas de miniaturización, mayor rendimiento y eficiencia energética en sectores como la electrónica de consumo, la automoción, las telecomunicaciones y los centros de datos. A partir de 2025, el mercado global para el embalaje de microelectrónica de chip apilados está experimentando un sólido crecimiento, impulsado por la proliferación de dispositivos 5G, aplicaciones de inteligencia artificial (IA) y el Internet de las Cosas (IoT).

Según Yole Group, se proyecta que el mercado de embalaje avanzado, que incluye soluciones de chip apilados, alcanzará más de $50 mil millones para 2025, con arquitecturas de chip apilados representando una parte significativa debido a su adopción en lógica de alta gama, memoria e integración heterogénea. La demanda de memoria de alto ancho de banda (HBM), 3D NAND y soluciones de sistema-en-paquete (SiP) está acelerando el cambio hacia configuraciones de chip apilados, ya que estas permiten una mayor densidad de interconexión y un mejor rendimiento eléctrico en comparación con el embalaje 2D tradicional.

Los principales actores de la industria, como TSMC, Samsung Electronics e Intel Corporation, están invirtiendo fuertemente en investigación y desarrollo para avanzar en tecnologías de vía a través del silicio (TSV) y embalaje a nivel de oblea (WLP), que son fundamentales para la integración de chips apilados. Estas innovaciones están permitiendo la producción de dispositivos más pequeños, rápidos y más eficientes energéticamente, particularmente en aplicaciones de computación de alto rendimiento y móviles.

Regionalmente, Asia-Pacífico domina el mercado de embalaje de microelectrónica de chip apilados, liderado por centros manufactureros en Taiwán, Corea del Sur y China. La región se beneficia de una sólida cadena de suministro de semiconductores y de inversiones agresivas en instalaciones de embalaje de próxima generación. Norteamérica y Europa también están viendo una adopción creciente, particularmente en electrónica automotriz e infraestructura de centros de datos, donde las soluciones de chip apilados son críticas para cumplir con estrictos requisitos de rendimiento y confiabilidad.

Mirando hacia 2025, se espera que el mercado de embalaje de microelectrónica de chip apilados mantenga una tasa de crecimiento anual compuesta (CAGR) de dos dígitos, impulsada por avances tecnológicos continuos y el implacable impulso por la miniaturización de dispositivos. Sin embargo, desafíos como la gestión térmica, optimización de rendimientos y restricciones en la cadena de suministro siguen siendo puntos focales para los actores de la industria que buscan capitalizar este dinámico segmento de mercado.

Tendencias Tecnológicas Clave en el Embalaje de Microelectrónica de Chip Apilados

El embalaje de microelectrónica de chip apilados está a la vanguardia de la innovación en semiconductores, permitiendo un mayor rendimiento de los dispositivos, funcionalidades aumentadas y factores de forma reducidos al integrar verticalmente múltiples chips semiconductores dentro de un solo paquete. A medida que la industria avanza hacia 2025, varias tendencias tecnológicas clave están dando forma a la evolución y adopción de soluciones de chip apilados.

- Integración Avanzada de Vías a Través del Silicio (TSV): La tecnología TSV sigue siendo central en las arquitecturas de chip apilados, proporcionando interconexiones verticales de alta densidad. Los avances recientes se centran en reducir el diámetro y el paso de las vías, lo que mejora la integridad de la señal y la eficiencia energética. Fundiciones líderes como TSMC y Samsung Electronics están impulsando la escalabilidad de TSV para soportar memoria de alto ancho de banda (HBM3) y la integración de lógica-memoria para aplicaciones de IA y computación de alto rendimiento.

- Integración Heterogénea: La tendencia hacia la integración de chiplets diversos—lógica, memoria, analógica y RF—dentro de un solo paquete apilado se está acelerando. Este enfoque permite la optimización a nivel de sistema y apoya la creciente demanda de circuitos integrados específicos de aplicación (ASIC) en centros de datos, automoción y dispositivos móviles. Foveros de Intel y 3D V-Cache de AMD ejemplifican la adopción comercial del apilamiento heterogéneo.

- Embalaje a Nivel de Oblea (WLP) y Tecnologías de Fan-Out: El apilamiento a nivel de oblea y el embalaje fan-out a nivel de panel están ganando tracción por su capacidad de ofrecer pasos de interconexión más finos y un rendimiento térmico mejorado. ASE Technology Holding y Amkor Technology están invirtiendo en líneas avanzadas de WLP para satisfacer la demanda de electrónica de consumo y automotriz compacta y de alto rendimiento.

- Innovaciones en Gestión Térmica: A medida que las densidades de potencia aumentan, la disipación efectiva del calor se vuelve crítica. Nuevos materiales (por ejemplo, compuestos de diamante, TIMs avanzados) y la refrigeración microfluídica integrada están siendo explorados para abordar los cuellos de botella térmicos en los paquetes de chip apilados, como se destaca en informes de mercado recientes de Yole Group.

- Automatización del Diseño y Soluciones de Prueba: La complejidad de las arquitecturas de chip apilados está impulsando la adopción de herramientas avanzadas de automatización de diseño electrónico (EDA) y metodologías de auto-prueba integrada (BIST). Empresas como Synopsys y Cadence Design Systems están desarrollando soluciones para simplificar el diseño, verificación y optimización de rendimientos de IC 3D.

Se espera que estas tendencias tecnológicas aceleren la adopción del embalaje de microelectrónica de chip apilados en 2025, apoyando aplicaciones de próxima generación en IA, 5G, automoción y computación de borde.

Panorama Competitivo y Principales Actores

El panorama competitivo del mercado de embalaje de microelectrónica de chip apilados en 2025 está caracterizado por una intensa innovación, asociaciones estratégicas y un enfoque en tecnologías de integración avanzada. El embalaje de chip apilados, que permite la integración vertical de múltiples chips semiconductores dentro de un solo paquete, es un habilitador crítico para la computación de alto rendimiento, dispositivos móviles y aplicaciones emergentes como la inteligencia artificial (IA) y las comunicaciones 5G.

Los principales actores de este mercado incluyen Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation y Amkor Technology. Estas empresas se han establecido como pioneras en soluciones de embalaje avanzadas, aprovechando su experiencia en fabricación de obleas, integración 3D y tecnologías de sistema-en-paquete (SiP).

TSMC continúa liderando con sus plataformas de embalaje 3D avanzadas, como CoWoS (Chip-on-Wafer-on-Substrate) y SoIC (System on Integrated Chips), que son ampliamente adoptadas para computación de alto rendimiento y aceleradores de IA. Samsung Electronics ha hecho importantes avances con su tecnología X-Cube (eXtended-Cube), que permite la integración de memoria de alta densidad y alto ancho de banda para aplicaciones móviles y de servidores de próxima generación. Intel está avanzando en su tecnología de apilamiento 3D Foveros, que permite la integración heterogénea de chips de lógica y memoria, apoyando el impulso de la compañía hacia los mercados de IA y centros de datos.

Proveedores de ensamblaje y prueba de semiconductores subcontratados (OSAT) como Amkor Technology y ASE Technology Holding también son actores clave, ofreciendo una amplia gama de servicios de embalaje de chip apilados a empresas de semiconductores sin fábrica y fabricantes de dispositivos integrados (IDMs). Estos OSAT están invirtiendo en líneas de embalaje avanzadas y colaborando con fundiciones para acelerar el tiempo de comercialización de soluciones multichip complejas.

- TSMC: Liderazgo en plataformas CoWoS y SoIC para IA y HPC.

- Samsung Electronics: Tecnología X-Cube para integración de memoria de alto ancho de banda.

- Intel Corporation: Apilamiento 3D Foveros para integración heterogénea.

- Amkor Technology y ASE Technology Holding: Servicios OSAT avanzados para soluciones de chip apilados.

A medida que la demanda de miniaturización y rendimiento se intensifica, se espera que el panorama competitivo vea una mayor consolidación, con los principales actores invirtiendo fuertemente en I+D y asociaciones del ecosistema para mantener su ventaja tecnológica en el embalaje de microelectrónica de chip apilados.

Pronósticos de Crecimiento del Mercado (2025–2030): CAGR, Análisis de Ingresos y Volumen

Se espera que el mercado de embalaje de microelectrónica de chip apilados experimente un sólido crecimiento entre 2025 y 2030, impulsado por la creciente demanda de dispositivos electrónicos compactos y de alto rendimiento en sectores como la electrónica de consumo, la automoción, las telecomunicaciones y la atención médica. Según proyecciones de MarketsandMarkets, se espera que el mercado global de IC 3D y embalaje de chip apilados registre una tasa de crecimiento anual compuesta (CAGR) de aproximadamente 12-14% durante este período. Esta trayectoria de crecimiento se apoya en la adopción creciente de soluciones de embalaje avanzadas para abordar las limitaciones de las arquitecturas 2D tradicionales, particularmente en términos de eficiencia energética, factor de forma y ancho de banda de datos.

Las proyecciones de ingresos indican que el mercado de embalaje de microelectrónica de chip apilados podría superar los 15 mil millones de USD para 2030, desde un estimado de 7.5 mil millones de USD en 2025. Este aumento se atribuye a la proliferación de aplicaciones que requieren integración de alta densidad, como aceleradores de inteligencia artificial (IA), infraestructura 5G y dispositivos de computación en el borde. Se anticipa que la región de Asia-Pacífico, liderada por países como China, Corea del Sur y Taiwán, dominará la cuota de mercado, representando más del 50% de los ingresos globales, debido a la concentración de instalaciones de fabricación y embalaje de semiconductores en la región (Gartner).

En términos de volumen, se proyecta que el número de unidades de chip apilados enviadas crecerá a una tasa compuesta anual (CAGR) del 13-15% de 2025 a 2030. Esta expansión de volumen es impulsada por el rápido lanzamiento de teléfonos inteligentes de próxima generación, dispositivos portátiles y electrónica automotriz, todos los cuales requieren soluciones de embalaje compactas y de alto rendimiento. Notablemente, se espera que el sector automotriz experimente el crecimiento más rápido en volumen, ya que los vehículos eléctricos (EVs) y los sistemas avanzados de asistencia al conductor (ADAS) dependen cada vez más de arquitecturas de chip apilados para mejorar el poder computacional y la confiabilidad (Yole Group).

- CAGR (2025–2030): 12–14%

- Ingresos (2030): >15 mil millones de USD

- CAGR de Volumen (2025–2030): 13–15%

- Principales Impulsores del Crecimiento: IA, 5G, electrónica automotriz, miniaturización

- Región Líder: Asia-Pacífico

Análisis del Mercado Regional: Norteamérica, Europa, Asia-Pacífico y Resto del Mundo

El mercado global de embalaje de microelectrónica de chip apilados está presenciando un crecimiento dinámico, con tendencias regionales moldeadas por avances tecnológicos, demanda de los usuarios finales y desarrollos en la cadena de suministro. En 2025, las regiones de Norteamérica, Europa, Asia-Pacífico y el Resto del Mundo (RoW) presentan características y motores de crecimiento distintos.

- Norteamérica: El mercado norteamericano está impulsado por robustas inversiones en fabricación avanzada de semiconductores y la fuerte presencia de firmas tecnológicas líderes. El enfoque de la región en computación de alto rendimiento, infraestructura 5G y electrónica automotriz está impulsando la demanda de soluciones de embalaje de chips apilados. Estados Unidos, en particular, se beneficia de iniciativas gubernamentales para fortalecer la producción doméstica de chips, como se observa en la Ley CHIPS, que se espera acelere la adopción de tecnologías de embalaje avanzadas en 2025 (Asociación de la Industria de Semiconductores).

- Europa: El mercado de embalaje de microelectrónica de chip apilados en Europa se caracteriza por un enfoque en aplicaciones automotrices, automatización industrial e IoT. El impulso de la región hacia la soberanía tecnológica y la Ley Europea de Chips están fomentando inversiones en ecosistemas locales de semiconductores. Alemania y Francia lideran en I+D y producción piloto, con un creciente énfasis en dispositivos energéticamente eficientes y miniaturizados (Asociación Europea de Fabricantes de Componentes Electrónicos).

- Asia-Pacífico: Asia-Pacífico sigue siendo el mercado más grande y de más rápido crecimiento para el embalaje de chips apilados, impulsado por la dominancia de países como China, Corea del Sur, Taiwán y Japón en fabricación y ensamblaje de semiconductores. La proliferación de electrónica de consumo, teléfonos inteligentes y dispositivos habilitados para IA está alimentando la demanda. Las principales fundiciones y proveedores de OSAT (ensamblaje y prueba de semiconductores subcontratados) en la región están aumentando sus inversiones en empaques 2.5D/3D e integración heterogénea para satisfacer la demanda global (SEMI).

- Resto del Mundo (RoW): Aunque más pequeño en escala, el segmento de RoW—que incluye América Latina, Oriente Medio y África—está adoptando gradualmente el embalaje de chips apilados, principalmente para telecomunicaciones y aplicaciones industriales emergentes. El crecimiento está respaldado por una digitalización creciente y por iniciativas tecnológicas lideradas por el gobierno, aunque la región enfrenta desafíos relacionados con la infraestructura y la mano de obra calificada (Gartner).

En general, se espera que 2025 vea una continua diversificación regional en el embalaje de microelectrónica de chip apilados, con Asia-Pacífico liderando en volumen, Norteamérica y Europa enfocándose en innovación y autonomía estratégica, y las regiones de RoW aumentando gradualmente la adopción a medida que la transformación digital acelera globalmente.

Perspectivas Futuras: Aplicaciones Emergentes y Puntos de Inversión Clave

Las perspectivas futuras para el embalaje de microelectrónica de chip apilados en 2025 están moldeadas por rápidos avances en integración de semiconductores, la proliferación de IA y computación de alto rendimiento, y la creciente demanda de dispositivos miniaturizados y energéticamente eficientes. El embalaje de chip apilados, que implica la integración vertical de múltiples chips semiconductores dentro de un solo paquete, está listo para desempeñar un papel fundamental en habilitar la electrónica de próxima generación en varios sectores de alto crecimiento.

Las aplicaciones emergentes son especialmente prominentes en centros de datos, infraestructura 5G y computación en el borde. La necesidad de un mayor ancho de banda y menor latencia en estos entornos está impulsando la adopción de soluciones de chip apilados 2.5D y 3D, que ofrecen una mejor densidad de interconexión y reducción de pérdidas de señal en comparación con el embalaje tradicional. Por ejemplo, los centros de datos de hiperescala están aprovechando cada vez más la memoria de alto ancho de banda (HBM) y el apilamiento de lógica-sobre-memoria para acelerar cargas de trabajo de IA y análisis de grandes datos, una tendencia destacada en análisis recientes por Gartner y IDC.

La electrónica de consumo, particularmente los smartphones y dispositivos portátiles, sigue siendo un importante foco de inversión. El impulso hacia dispositivos más delgados y ligeros con funcionalidad mejorada está alimentando la demanda de técnicas de embalaje avanzadas, como el vía a través del silicio (TSV) y el apilamiento a nivel de oblea. Según Yole Group, se espera que el mercado de embalaje de chip apilados en dispositivos móviles e IoT vea un crecimiento de dos dígitos hasta 2025, a medida que los OEM buscan integrar más características sin aumentar la huella del dispositivo.

La electrónica automotriz representa otra área de aplicación emergente, especialmente a medida que los vehículos eléctricos (EVs) y los sistemas de conducción autónoma requieren módulos de computación compactos y de alta confiabilidad. El embalaje de chip apilados permite la integración de sensores, procesadores y memoria en un solo módulo, apoyando el procesamiento de datos en tiempo real y sistemas de asistencia avanzada al conductor (ADAS). McKinsey & Company proyecta que el contenido de semiconductores automotrices superará el crecimiento general de los vehículos, con soluciones de chip apilados desempeñando un papel central.

- Puntos de inversión clave para 2025 incluyen memoria avanzada (HBM, 3D NAND), aceleradores de IA, estaciones base 5G/6G y módulos ADAS automotrices.

- Se espera que Asia-Pacífico, liderado por Taiwán y Corea del Sur, domine las inversiones en fabricación e I+D, según lo señalado por SEMI.

- Las asociaciones estratégicas entre fundiciones, OSAT y proveedores de herramientas EDA están acelerando la innovación y comercialización de tecnologías de chip apilados.

En resumen, el embalaje de microelectrónica de chip apilados está preparado para respaldar avances críticos en computación, conectividad y movilidad en 2025, con una sólida inversión e innovación centrada en dominios de aplicación de alto crecimiento y alto valor.

Desafíos, Riesgos y Oportunidades Estratégicas

El embalaje de microelectrónica de chip apilados, un habilitador crítico para sistemas electrónicos de alta densidad y alto rendimiento, enfrenta un complejo panorama de desafíos y riesgos en 2025, pero también presenta oportunidades estratégicas significativas para los actores de la industria. El principal desafío técnico sigue siendo la gestión térmica. A medida que más chips se integran verticalmente, la disipación de calor se vuelve cada vez más problemática, arriesgando la confiabilidad del dispositivo y la degradación del rendimiento. Se están explorando materiales avanzados de interfaz térmica y diseños innovadores de dispersores de calor, pero su integración agrega costo y complejidad al proceso de fabricación (SEMI).

Los riesgos de rendimiento y confiabilidad también se ven aumentados en las arquitecturas de chip apilados. El número incrementado de interconexiones, como las vías a través del silicio (TSVs), eleva la probabilidad de defectos, impactando el rendimiento global. Además, las tensiones mecánicas inducidas durante el apilamiento y embalaje pueden provocar fracturas o delaminación de los chips, especialmente a medida que el tamaño de los paquetes se reduce y la cantidad de chips aumenta. Estas preocupaciones de confiabilidad requieren protocolos rigurosos de prueba e inspección, lo que puede extender el tiempo de comercialización e inflar costos (Yole Group).

La complejidad de la cadena de suministro es otro riesgo significativo. El embalaje de chip apilados a menudo requiere colaboración entre múltiples proveedores para la fabricación de obleas, adelgazado de chips, apilamiento y ensamblaje final. Las interrupciones en cualquier segmento—como escasez de sustratos avanzados o retrasos en equipos de unión de alta precisión—pueden afectar toda la línea de producción. Las prácticas geopolíticas en curso y las escaseces de material observadas en los últimos años han subrayado la vulnerabilidad de estas intrincadas cadenas de suministro (Gartner).

A pesar de estos desafíos, abundan las oportunidades estratégicas. La creciente demanda de memoria de alto ancho de banda, aceleradores de IA e infraestructura 5G/6G está impulsando la inversión en soluciones de chip apilados. Las empresas que puedan innovar en áreas como la integración heterogénea, arquitecturas de chiplet y gestión térmica avanzada tienen la posibilidad de captar una parte significativa del mercado. Las asociaciones estratégicas entre fundiciones, OSAT (ensamblaje y prueba de semiconductores subcontratados) y proveedores de herramientas EDA están emergiendo como un factor clave de éxito, permitiendo soluciones integrales que abordan riesgos tanto técnicos como de cadena de suministro (TSMC).

En resumen, aunque el embalaje de microelectrónica de chip apilados en 2025 está cargado de riesgos técnicos, de confiabilidad y de cadena de suministro, también ofrece oportunidades de crecimiento sustanciales para quienes puedan navegar por el paisaje evolutivo con innovación y colaboración estratégica.

Fuentes y Referencias

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Asociación de la Industria de Semiconductores

- IDC

- McKinsey & Company