Marktbericht für die Mikroelektronikverpackung mit gestapelten Chips 2025: Wachstum, Technologiewechsel und strategische Einblicke für die nächsten 5 Jahre. Entdecken Sie wichtige Trends, Prognosen und Wettbewerbskräfte, die die Branche prägen.

- Zusammenfassung & Marktübersicht

- Wichtige Technologietrends in der Mikroelektronikverpackung mit gestapelten Chips

- Wettbewerbslandschaft und führende Akteure

- Marktwachstumsprognosen (2025–2030): CAGR, Umsatz- und Mengenanalyse

- Regionale Marktanalyse: Nordamerika, Europa, Asien-Pazifik und Rest der Welt

- Zukünftige Perspektiven: Neue Anwendungen und Investitionsschwerpunkte

- Herausforderungen, Risiken und strategische Chancen

- Quellen & Referenzen

Zusammenfassung & Marktübersicht

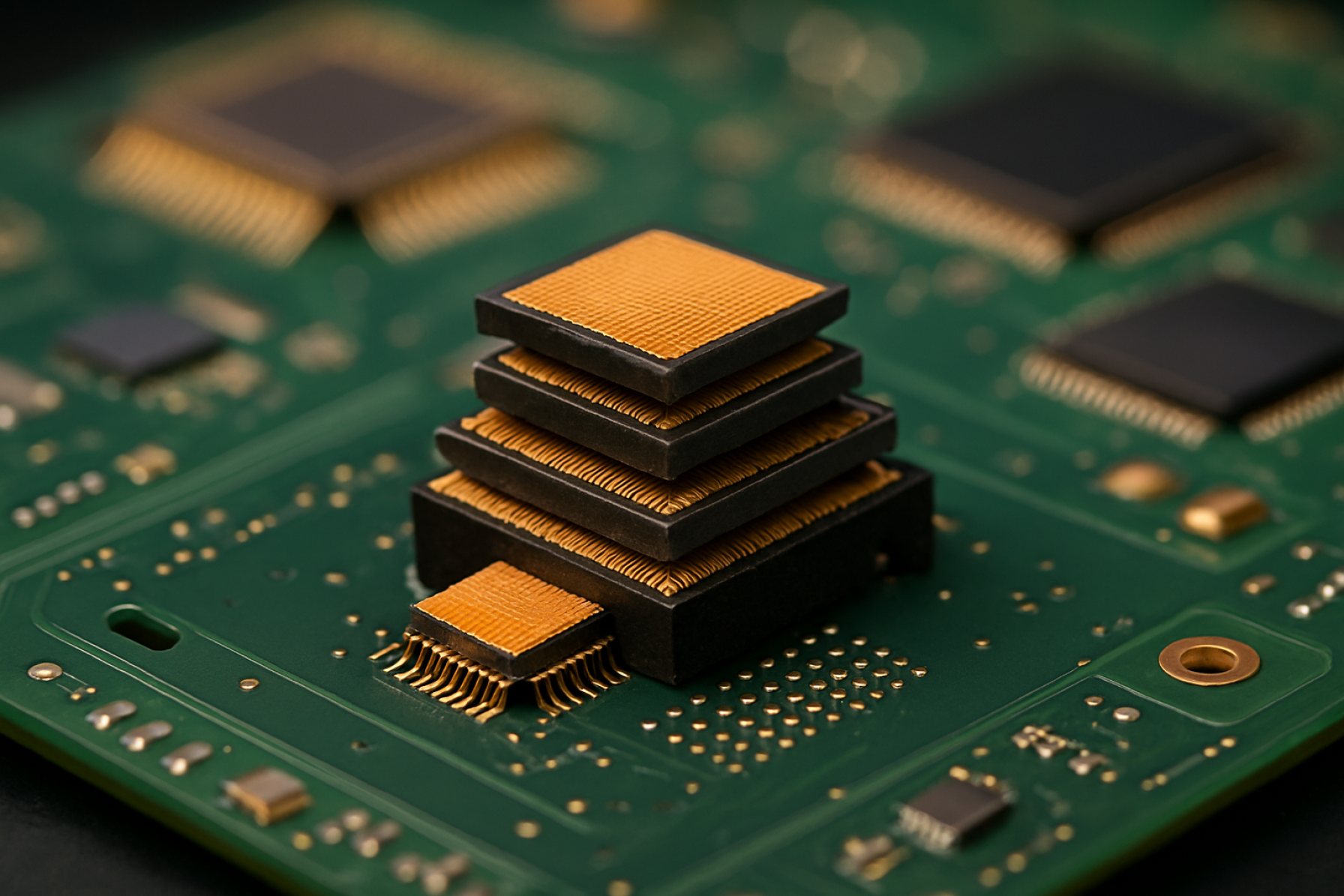

Die Mikroelektronikverpackung mit gestapelten Chips bezieht sich auf die Integration mehrerer Halbleiterchips innerhalb eines einzigen Pakets, die vertikal angeordnet sind, um Platz, Leistung und Funktionalität zu optimieren. Diese fortschrittliche Verpackungstechnologie ist entscheidend, um den steigenden Anforderungen an Miniaturisierung, höhere Leistung und Energieeffizienz in Sektoren wie Unterhaltungselektronik, Automobilindustrie, Telekommunikation und Rechenzentren gerecht zu werden. Im Jahr 2025 erlebt der globale Markt für Mikroelektronikverpackungen mit gestapelten Chips ein robustes Wachstum, getrieben durch die Verbreitung von 5G-Geräten, Anwendungen der künstlichen Intelligenz (KI) und dem Internet der Dinge (IoT).

Laut Yole Group wird der Markt für fortschrittliche Verpackungen, zu dem auch Lösungen mit gestapelten Chips gehören, bis 2025 über 50 Milliarden USD erreichen, wobei die Architekturen mit gestapelten Chips einen erheblichen Anteil ausmachen, da sie in High-End-Logik, Speicher und heterogene Integration angenommen werden. Die Nachfrage nach hochbandbreitigen Speicherlösungen (HBM), 3D NAND und System-in-Package (SiP)-Lösungen beschleunigt den Übergang zu gestapelten Chip-Konfigurationen, da diese eine höhere Verbindungsdichte und verbesserte elektrische Leistung im Vergleich zu herkömmlichen 2D-Verpackungen ermöglichen.

Führende Unternehmen der Branche wie TSMC, Samsung Electronics und Intel Corporation investieren umfassend in Forschung und Entwicklung, um Technologien für Durch-Silizium-Verbindungen (TSV) und wafer-level packaging (WLP) voranzutreiben, die für die Integration gestapelter Chips grundlegend sind. Diese Innovationen ermöglichen die Herstellung kleinerer, schnellerer und energieeffizienterer Geräte, insbesondere im Bereich des Hochleistungsrechnens und mobiler Anwendungen.

Regional dominieren Asien-Pazifik bei der Mikroelektronikverpackung mit gestapelten Chips, angeführt von Produktionszentren in Taiwan, Südkorea und China. Die Region profitiert von einer starken Halbleiter-Lieferkette und aggressiven Investitionen in Einrichtungen für die nächste Generation der Verpackung. Nordamerika und Europa verzeichnen ebenfalls eine zunehmende Verbreitung, insbesondere in der Automobilindustrie und der Datenzentrum-Infrastruktur, wo Lösungen mit gestapelten Chips entscheidend sind, um strengen Leistungs- und Zuverlässigkeitsanforderungen gerecht zu werden.

Mit Blick auf 2025 wird erwartet, dass der Markt für Mikroelektronikverpackungen mit gestapelten Chips eine zweistellige jährliche Wachstumsrate (CAGR) aufrechterhält, unterstützt durch anhaltende technologische Fortschritte und den unaufhörlichen Drang nach Miniaturisierung. Herausforderungen wie Wärmemanagement, Ertragsoptimierung und Einschränkungen in der Lieferkette bleiben jedoch zentrale Punkte für die Akteure der Branche, die von diesem dynamischen Marktsegment profitieren möchten.

Wichtige Technologietrends in der Mikroelektronikverpackung mit gestapelten Chips

Die Mikroelektronikverpackung mit gestapelten Chips steht an der Spitze der Halbleiterinnovation und ermöglicht höhere Geräteleistungen, gesteigerte Funktionalität und reduzierte Formfaktoren, indem mehrere Halbleiterchips in einem einzigen Paket vertikal integriert werden. Während sich die Branche auf 2025 zubewegt, prägen mehrere wichtige Technologietrends die Evolution und Akzeptanz von Lösungen mit gestapelten Chips.

- Erweiterte Durch-Silizium-Verbindung (TSV) Integration: Die TSV-Technologie bleibt zentral für Architekturen mit gestapelten Chips und bietet hochdichte vertikale Verbindungen. Jüngste Fortschritte konzentrieren sich auf die Verringerung des Durchmessers und des Abstands der Verbindungen, was die Signalintegrität und Energieeffizienz verbessert. Führende Foundries wie TSMC und Samsung Electronics treiben die Skalierung von TSV voran, um hochbandbreitige Speicherlösungen (HBM3) und Logik-Speicher-Integration für KI- und HPC-Anwendungen zu unterstützen.

- Heterogene Integration: Der Trend zur Integration verschiedener Chiplets – Logik, Speicher, analog und RF – innerhalb eines einzigen gestapelten Pakets beschleunigt sich. Dieser Ansatz ermöglicht eine Systemoptimierung und unterstützt die wachsende Nachfrage nach anwendungsspezifischen integrierten Schaltungen (ASICs) in Rechenzentren, der Automobilindustrie und mobilen Geräten. Intels Foveros und AMDs 3D V-Cache sind Beispiele für die kommerzielle Annahme des heterogenen Stapelns.

- Wafer-Level Packaging (WLP) und Fan-Out-Technologien: Wafer-Level-Stapeln und Fan-Out-Panel-Level-Verpackungen gewinnen an Bedeutung für ihre Fähigkeit, feinere Verbindungsabstände und verbesserte thermische Leistung zu liefern. ASE Technology Holding und Amkor Technology investieren in fortschrittliche WLP-Linien, um der Nachfrage nach kompakten, leistungsstarken elektronischen Geräten im Verbraucher- und Automobilbereich gerecht zu werden.

- Innovationen im Wärmemanagement: Mit steigender Leistungsdichte wird eine effektive Wärmeabfuhr entscheidend. Neue Materialien (z. B. Diamantverbundstoffe, fortschrittliche TIMs) und integrierte mikrofluidische Kühlung werden erforscht, um thermische Engpässe in gestapelten Chip-Paketen zu adressieren, wie in den aktuellen Marktberichten der Yole Group hervorgehoben.

- Designautomatisierung und Testlösungen: Die Komplexität von Architekturen mit gestapelten Chips treibt die Akzeptanz fortschrittlicher Tools zur elektronischen Designautomatisierung (EDA) und Built-in Self-Test (BIST)-Methoden voran. Unternehmen wie Synopsys und Cadence Design Systems entwickeln Lösungen zur Rationalisierung des 3D-IC-Designs, der Verifizierung und der Ertragsoptimierung.

Diese Technologietrends werden voraussichtlich die Akzeptanz von Mikroelektronikverpackungen mit gestapelten Chips im Jahr 2025 beschleunigen und nächste Generationen von Anwendungen in den Bereichen KI, 5G, Automobilindustrie und Edge-Computing unterstützen.

Wettbewerbslandschaft und führende Akteure

Die Wettbewerbslandschaft des Marktes für Mikroelektronikverpackungen mit gestapelten Chips im Jahr 2025 ist geprägt von intensiver Innovation, strategischen Partnerschaften und einem Fokus auf fortschrittliche Integrationstechnologien. Die Verpackung mit gestapelten Chips, die die vertikale Integration mehrerer Halbleiterchips innerhalb eines einzigen Pakets ermöglicht, ist ein entscheidender Faktor für Hochleistungsrechnen, mobile Geräte und neue Anwendungen wie künstliche Intelligenz (KI) und 5G-Kommunikation.

Zu den führenden Akteuren in diesem Markt gehören Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation und Amkor Technology. Diese Unternehmen haben sich als Pioniere in der Entwicklung fortschrittlicher Verpackungslösungen etabliert und nutzen ihre Expertise in der Wafer-Fabrikation, 3D-Integration und System-in-Package (SiP)-Technologien.

TSMC führt weiterhin mit seinen fortschrittlichen 3D-Verpackungsplattformen, wie CoWoS (Chip-on-Wafer-on-Substrate) und SoIC (System on Integrated Chips), die weithin für Hochleistungsrechnen und KI-Beschleuniger übernommen werden. Samsung Electronics hat bedeutende Fortschritte mit seiner X-Cube (eXtended-Cube)-Technologie gemacht, die eine hochdichte, hochbandbreitige Speicherintegration für Anwendungen der nächsten Generation im Mobil- und Serverbereich ermöglicht. Intel baut seine Foveros 3D-Stapeltechnologie weiter aus, die eine heterogene Integration von Logik- und Speicherschips ermöglicht und den Vorstoß des Unternehmens in den Märkten für KI und Rechenzentren unterstützt.

Ausgelagerte Halbleiterherstellungs- und Testanbieter (OSAT) wie Amkor Technology und ASE Technology Holding sind ebenfalls wichtige Akteure und bieten ein breites Portfolio von Verpackungsdiensten mit gestapelten Chips für fabless Halbleiterunternehmen und integrierte Gerätehersteller (IDMs) an. Diese OSATs investieren in fortschrittliche Verpackungslinien und arbeiten mit Foundries zusammen, um die Markteinführungszeit für komplexe Multi-Chip-Lösungen zu verkürzen.

- TSMC: Führend in CoWoS- und SoIC-Plattformen für KI und HPC.

- Samsung Electronics: X-Cube-Technologie für hochbandbreitige Speicherintegration.

- Intel Corporation: Foveros 3D-Stapelung für heterogene Integration.

- Amkor Technology und ASE Technology Holding: Fortgeschrittene OSAT-Dienste für Lösungen mit gestapelten Chips.

Da der Bedarf an Miniaturisierung und Leistung steigt, wird die Wettbewerbslandschaft voraussichtlich weitere Konsolidierungen erleben, wobei führende Akteure stark in Forschung & Entwicklung und Ökosystempartnerschaften investieren, um ihren technologischen Vorsprung in der Mikroelektronikverpackung mit gestapelten Chips aufrechtzuerhalten.

Marktwachstumsprognosen (2025–2030): CAGR, Umsatz- und Mengenanalyse

Der Markt für Mikroelektronikverpackungen mit gestapelten Chips steht zwischen 2025 und 2030 vor robustem Wachstum, getrieben durch die steigende Nachfrage nach leistungsstarken, miniaturisierten elektronischen Geräten in Sektoren wie Unterhaltungselektronik, Automobilindustrie, Telekommunikation und Gesundheitswesen. Laut Prognosen von MarketsandMarkets wird der globale 3D-IC- und gestapelte Chips-Verpackungsmarkt während dieses Zeitraums voraussichtlich eine jährliche Wachstumsrate (CAGR) von rund 12–14 % erreichen. Diese Wachstumskurve wird durch die wachsende Akzeptanz fortschrittlicher Verpackungslösungen untermauert, um die Einschränkungen traditioneller 2D-Architekturen zu adressieren, insbesondere hinsichtlich Energieeffizienz, Formfaktor und Datenbandbreite.

Die Umsatzprognosen deuten darauf hin, dass der Markt für Mikroelektronikverpackungen mit gestapelten Chips bis 2030 mehr als 15 Milliarden USD überschreiten könnte, gegenüber geschätzten 7,5 Milliarden USD im Jahr 2025. Dieser Anstieg wird durch die Verbreitung von Anwendungen, die eine hochdichte Integration erfordern, wie beispielsweise KI-Beschleuniger, 5G-Infrastruktur und Edge-Computing-Geräte, begünstigt. Die Region Asien-Pazifik, angeführt von Ländern wie China, Südkorea und Taiwan, wird voraussichtlich den Marktanteil dominieren und über 50 % der globalen Einnahmen ausmachen, da sich die Halbleiterfertigung und Verpackungseinrichtungen in der Region konzentrieren (Gartner).

In Bezug auf das Volumen wird die Anzahl der ausgelieferten Einheiten mit gestapelten Chips voraussichtlich von 2025 bis 2030 mit einer CAGR von 13–15 % wachsen. Diese Volumenausweitung wird durch die rasche Einführung von Next-Generation-Smartphones, Wearables und Automobil-Elektronik, die alle kompakte, leistungsstarke Verpackungslösungen benötigen, gefördert. Besonders die Automobilbranche wird voraussichtlich das schnellste Volumenwachstum erleben, da Elektrofahrzeuge (EVs) und fortschrittliche Fahrassistenzsysteme (ADAS) zunehmend auf Architekturen mit gestapelten Chips angewiesen sind, um die rechnerische Leistung und Zuverlässigkeit zu erhöhen (Yole Group).

- CAGR (2025–2030): 12–14 %

- Umsatz (2030): >15 Milliarden USD

- Volumen CAGR (2025–2030): 13–15 %

- Wachstumstreiber: KI, 5G, Automobil-Elektronik, Miniaturisierung

- Führende Region: Asien-Pazifik

Regionale Marktanalyse: Nordamerika, Europa, Asien-Pazifik und Rest der Welt

Der globale Markt für Mikroelektronikverpackungen mit gestapelten Chips erlebt dynamisches Wachstum, wobei regionale Trends durch technologische Fortschritte, die Nachfrage der Endanwender und Entwicklungen in der Lieferkette geprägt sind. Im Jahr 2025 weisen die Regionen Nordamerika, Europa, Asien-Pazifik und der Rest der Welt (RoW) jeweils unterschiedliche Marktmerkmale und Wachstumstreiber auf.

- Nordamerika: Der nordamerikanische Markt wird durch robuste Investitionen in fortschrittliche Halbleiterfertigung und eine starke Präsenz führender Technologieunternehmen getragen. Der Fokus der Region auf Hochleistungsrechnen, 5G-Infrastruktur und Elektronik im Automobilbereich treibt die Nachfrage nach Lösungen mit gestapelten Chips an. Die Vereinigten Staaten profitieren insbesondere von staatlichen Initiativen zur Stärkung der heimischen Chip-Produktion, wie im CHIPS Act zu sehen ist, der voraussichtlich die Einführung fortschrittlicher Verpackungstechnologien im Jahr 2025 beschleunigen wird (Semiconductor Industry Association).

- Europa: Der Markt für Mikroelektronikverpackungen mit gestapelten Chips in Europa ist geprägt von einem Fokus auf Automobil-, Industrieautomatisierungs- und IoT-Anwendungen. Der Technologiefortschritt in der Region sowie der European Chips Act fördern Investitionen in lokale Halbleiterökosysteme. Deutschland und Frankreich führen in Forschung und Entwicklung sowie der Pilotproduktion, wobei der Fokus auf energieeffizienten und miniaturisierten Geräten liegt (European Electronic Component Manufacturers Association).

- Asien-Pazifik: Asien-Pazifik bleibt der größte und am schnellsten wachsende Markt für gestapelte Verpackungen, angetrieben durch die Dominanz von Ländern wie China, Südkorea, Taiwan und Japan in der Halbleiterfertigung und -montage. Die Verbreitung von Unterhaltungselektronik, Smartphones und KI-fähigen Geräten fördert die Nachfrage. Große Foundries und OSAT-Anbieter (Outsourced Semiconductor Assembly and Test) in der Region erweitern ihre Investitionen in 2,5D/3D-Verpackungen und heterogene Integration, um der globalen Nachfrage gerecht zu werden (SEMI).

- Rest der Welt (RoW): Obwohl kleiner im Umfang, nimmt das RoW-Segment, einschließlich Lateinamerika, dem Nahen Osten und Afrika, allmählich Lösungen mit gestapelten Chips an, hauptsächlich für Telekommunikation und aufkommende industrielle Anwendungen. Das Wachstum wird durch zunehmende Digitalisierung und staatlich geförderte Technologieinitiativen unterstützt, obwohl die Region mit Herausforderungen im Bereich Infrastruktur und qualifizierte Arbeitskräfte konfrontiert ist (Gartner).

Insgesamt wird erwartet, dass 2025 eine weitere regionale Diversifizierung in der Mikroelektronikverpackung mit gestapelten Chips zu beobachten sein wird, wobei Asien-Pazifik in Bezug auf das Volumen führt, Nordamerika und Europa auf Innovation und strategische Autonomie fokussiert sind und RoW-Regionen allmählich die Akzeptanz erhöhen, da die digitale Transformation weltweit beschleunigt.

Zukünftige Perspektiven: Neue Anwendungen und Investitionsschwerpunkte

Die zukünftige Perspektive für die Mikroelektronikverpackung mit gestapelten Chips im Jahr 2025 wird durch die rasanten Fortschritte in der Halbleiterintegration, die Verbreitung von KI und Hochleistungsrechnen sowie die wachsende Nachfrage nach miniaturisierten, energieeffizienten Geräten geprägt. Die Mikroelektronikverpackung mit gestapelten Chips, die eine vertikale Integration mehrerer Halbleiterchips innerhalb eines einzigen Pakets umfasst, wird eine entscheidende Rolle bei der Ermöglichung der nächsten Generation von Elektronik in verschiedenen wachstumsstarken Sektoren spielen.

Neue Anwendungen sind insbesondere in Rechenzentren, 5G-Infrastrukturen und Edge-Verarbeitung hervorzuheben. Der Bedarf an höherer Bandbreite und geringerer Latenz in diesen Umgebungen treibt die Nutzung von 2,5D- und 3D-gestapelten Chiplösungen an, die eine verbesserte Verbindungsdichte und verringerte Signalverluste im Vergleich zu herkömmlichen Verpackungen bieten. So nutzen hyperscale Rechenzentren zunehmend hochbandbreitigen Speicher (HBM) und Logik-auf-Speicher-Stapelungen, um KI-Workloads und Big Data-Analysen zu beschleunigen, ein Trend, der in den aktuellen Analysen von Gartner und IDC hervorgehoben wird.

Die Unterhaltungselektronik, insbesondere Smartphones und Wearables, bleibt ein bedeutender Investitionsschwerpunkt. Der Drang nach dünneren, leichteren Geräten mit verbesserter Funktionalität fördert die Nachfrage nach fortschrittlichen Verpackungstechniken wie Durch-Silizium-Verbindungen (TSV) und Wafer-Level-Stapeln. Laut Yole Group wird erwartet, dass der Markt für Mikroelektronikverpackungen in mobilen und IoT-Geräten bis 2025 zweistellig wächst, da OEMs mehr Funktionen integrieren möchten, ohne den Gerätestandort zu vergrößern.

Die Elektronikbranche im Automobilsektor stellt ein weiteres aufkommendes Anwendungsgebiet dar, insbesondere da Elektrofahrzeuge (EVs) und autonome Fahrsysteme kompakte, zuverlässige Rechenmodule benötigen. Die Mikroelektronikverpackung mit gestapelten Chips ermöglicht die Integration von Sensoren, Prozessoren und Speicher in einem einzigen Modul, was die Verarbeitung von Echtzeitdaten und fortschrittliche Fahrerassistenzsysteme (ADAS) unterstützt. McKinsey & Company prognostiziert, dass der Halbleiterbedarf im Automobilbereich das Gesamtwachstum der Fahrzeuge übertreffen wird, wobei Lösungen mit gestapelten Chips eine zentrale Rolle spielen.

- Wichtige Investitionsschwerpunkte für 2025 umfassen fortschrittlichen Speicher (HBM, 3D NAND), KI-Beschleuniger, 5G/6G-Basisstationen und Module für ADAS im Automobilbereich.

- Asien-Pazifik, angeführt von Taiwan und Südkorea, wird voraussichtlich Fertigungs- und F&E-Investitionen dominieren, wie SEMI feststellt.

- Strategische Partnerschaften zwischen Foundries, OSATs und Systemintegratoren beschleunigen die Innovation und Kommerzialisierung von Technologien mit gestapelten Chips.

Zusammenfassend lässt sich sagen, dass die Mikroelektronikverpackung mit gestapelten Chips entscheidende Fortschritte in den Bereichen Computing, Konnektivität und Mobilität im Jahr 2025 unterstützen wird, mit robusten Investitionen und Innovationen, die auf wachstumsstarke, wertschöpfende Anwendungsbereiche fokussiert sind.

Herausforderungen, Risiken und strategische Chancen

Die Mikroelektronikverpackung mit gestapelten Chips, eine kritische Voraussetzung für hochdichte und leistungsstarke elektronische Systeme, sieht sich im Jahr 2025 einer komplexen Landschaft von Herausforderungen und Risiken gegenüber, bietet jedoch auch erhebliche strategische Chancen für die Akteure der Branche. Die Haupttechnische Herausforderung bleibt das Wärmemanagement. Mit der vertikalen Integration mehrerer Chips wird die Wärmeableitung zunehmend problematisch, was die Zuverlässigkeit und Leistung der Geräte gefährden kann. Fortschrittliche thermische Verbindungsmaterialien und innovative Wärmeverteiler-Designs werden erforscht, aber deren Integration erhöht die Kosten und Komplexität des Fertigungsprozesses (SEMI).

Ertrags- und Zuverlässigkeitsrisiken sind auch in Architekturen mit gestapelten Chips erhöht. Die erhöhte Anzahl von Verbindungen, wie Durch-Silizium-Verbindungen (TSVs), erhöht die Wahrscheinlichkeit von Fehlern, die den Gesamt-Ertrag beeinträchtigen können. Darüber hinaus können die mechanischen Spannungen, die während des Stapelns und der Verpackung entstehen, zu Rissen oder Delaminierungen der Chips führen, insbesondere wenn die Paketgrößen schrumpfen und die Chipanzahl steigt. Diese Zuverlässigkeitsbedenken erfordern strenge Test- und Inspektionsprotokolle, die die Markteinführungszeit verlängern und die Kosten erhöhen können (Yole Group).

Die Komplexität der Lieferkette ist ein weiteres bedeutendes Risiko. Die Verpackung mit gestapelten Chips erfordert häufig die Zusammenarbeit zwischen mehreren Anbietern für Wafer-Fabrikation, Chip-Dünnung, Stapelung und Endmontage. Störungen in einem beliebigen Segment – wie etwa Engpässe bei fortschrittlichen Substraten oder Verzögerungen bei hochpräzisen Bonding-Geräten – können den Produktionszeitplan erheblich beeinflussen. Die anhaltenden geopolitischen Spannungen und Materialengpässe der letzten Jahre haben die Verwundbarkeit dieser komplexen Lieferketten verdeutlicht (Gartner).

Trotz dieser Herausforderungen gibt es zahlreiche strategische Chancen. Die steigende Nachfrage nach hochbandbreitigem Speicher, KI-Beschleunigern und 5G/6G-Infrastruktur treibt die Investitionen in Lösungen mit gestapelten Chips voran. Unternehmen, die in Bereichen wie heterogene Integration, Chiplet-Architekturen und fortschrittlichem Wärmemanagement innovativ sein können, haben die Möglichkeit, erhebliche Marktanteile zu gewinnen. Strategische Partnerschaften zwischen Foundries, OSATs (Outsourced Semiconductor Assembly and Test) und EDA-Tool-Anbietern treten als Erfolgsfaktor hervor, indem sie End-to-End-Lösungen ermöglichen, die sowohl technische als auch Lieferkettenrisiken adressieren (TSMC).

Zusammenfassend lässt sich sagen, dass die Mikroelektronikverpackung mit gestapelten Chips im Jahr 2025 zwar mit technischen, Zuverlässigkeits- und Lieferkettenrisiken behaftet ist, jedoch auch beträchtliche Wachstumschancen für diejenigen bietet, die in der Lage sind, die sich entwickelnde Landschaft mit Innovation und strategischer Zusammenarbeit zu navigieren.

Quellen & Referenzen

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Semiconductor Industry Association

- IDC

- McKinsey & Company