Zpráva o trhu s mikroelektronickým balením stohovaných čipů 2025: Růst, technologické posuny a strategické informace na příštích 5 let. Prozkoumejte klíčové trendy, předpovědi a konkurenční dynamiku utvářející odvětví.

- Výkonný souhrn a přehled trhu

- Klíčové technologické trendy v mikroelektronickém balení stohovaných čipů

- Konkurenční prostředí a vedoucí hráči

- Předpovědi růstu trhu (2025–2030): CAGR, analýza příjmů a objemu

- Regionální analýza trhu: Severní Amerika, Evropa, Asie-Pacifik a zbytek světa

- Budoucí výhled: Vznikající aplikace a investiční hotspoty

- Výzvy, rizika a strategické příležitosti

- Zdroje a odkazy

Výkonný souhrn a přehled trhu

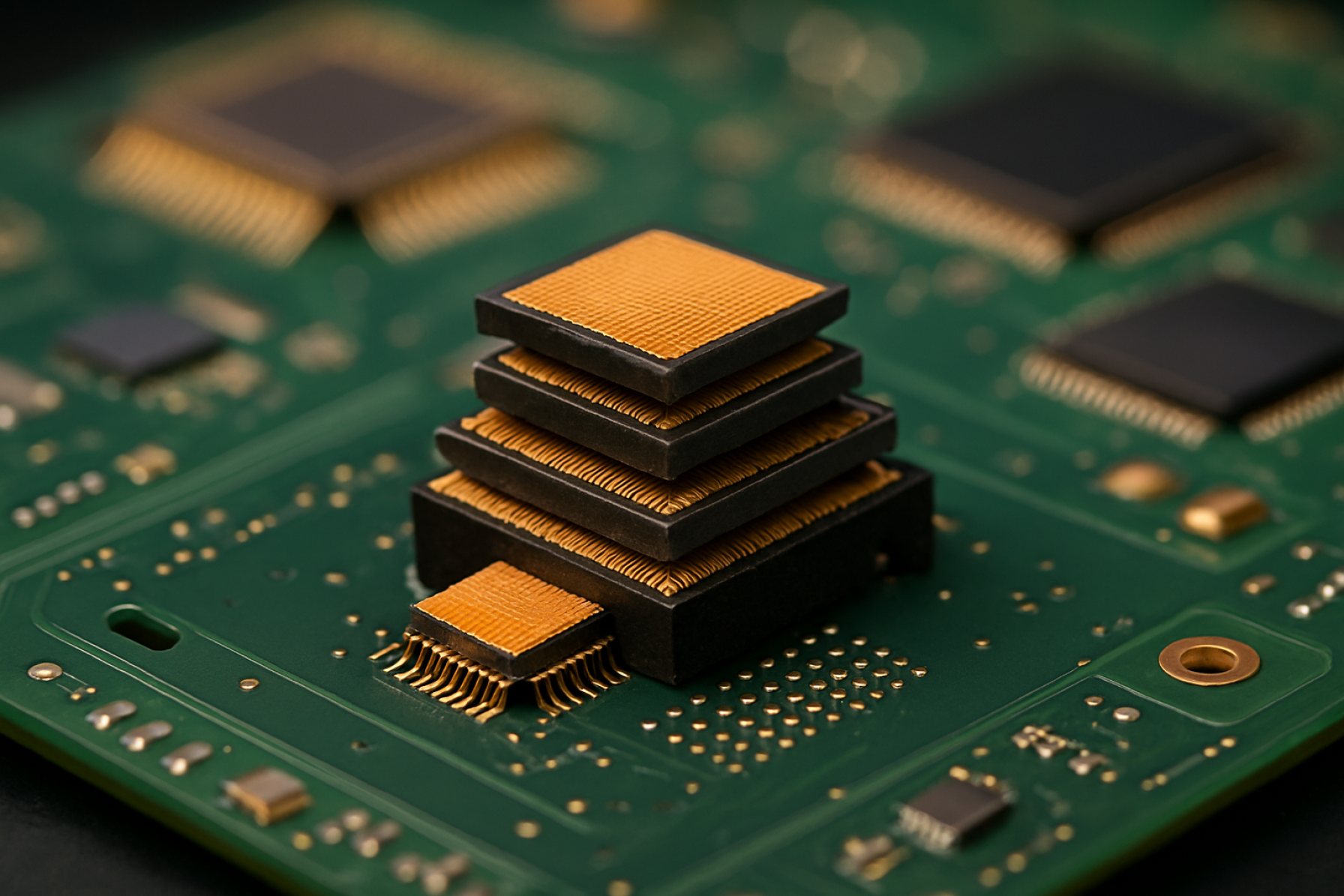

Mikroelektronické balení stohovaných čipů se týká integrace několika polovodičových čipů v rámci jednoho balení, uspořádaných vertikálně za účelem optimalizace prostoru, výkonu a funkčnosti. Tato pokročilá balicí technologie je klíčová pro splnění rostoucích požadavků na miniaturizaci, vyšší výkon a energetickou efektivitu v sektorech, jako je spotřební elektronika, automobilový průmysl, telekomunikace a datová centra. K roku 2025 zažívá globální trh s mikroelektronickým balením stohovaných čipů robustní růst, poháněný rozšířením zařízení 5G, aplikacemi umělé inteligence (AI) a Internetem věcí (IoT).

Podle Yole Group se očekává, že trh pokročilého balení, který zahrnuje stohovaná řešení, dosáhne do roku 2025 více než 50 miliard dolarů, přičemž architektury stohovaných čipů tvoří významný podíl díky jejich přijetí v high-end logice, paměti a heterogenní integraci. Poptávka po paměti s vysokou šířkou pásma (HBM), 3D NAND a systémových baleních (SiP) urychluje přechod na konfigurace stohovaných čipů, protože tyto umožňují vyšší hustotu propojení a lepší elektrický výkon ve srovnání s tradičním 2D balením.

Klíčoví hráči v odvětví, jako jsou TSMC, Samsung Electronics a Intel Corporation, investují významné prostředky do výzkumu a vývoje, aby pokročili v technologiích přes-silikonových propojení (TSV) a balení na úrovni waferu (WLP), které jsou základem pro integraci stohovaných čipů. Tyto inovace umožňují výrobu menších, rychlejších a energeticky efektivnějších zařízení, zejména v oblasti vysokovýkonného počítačového a mobilního použití.

Pokud jde o regionální rozložení, Asie-Pacifik dominuje trhu s mikroelektronickým balením stohovaných čipů, vedená výrobními centry na Tchaj-wanu, v Jižní Koreji a Číně. Region má prospěch z silného dodavatelského řetězce pro polovodiče a agresivních investic do zařízení pro příští generaci balení. Severní Amerika a Evropa také zaznamenávají zvýšené přijetí, zejména v automobilové elektronice a infrastruktuře datových center, kde jsou stohovaná řešení kritická pro splnění přísných požadavků na výkon a spolehlivost.

S ohledem na rok 2025 se očekává, že trh s mikroelektronickým balením stohovaných čipů si udrží dvoucifernou roční míru růstu (CAGR), poháněnou pokračujícími technologickými pokroky a neúprosným tlakem na miniaturizaci zařízení. Nicméně výzvy, jako je správa tepla, optimalizace výnosů a omezení dodavatelského řetězce, zůstávají klíčovými body pro zainteresované strany v odvětví, které se snaží využít potenciál tohoto dynamického segmentu trhu.

Klíčové technologické trendy v mikroelektronickém balení stohovaných čipů

Mikroelektronické balení stohovaných čipů je v popředí inovací v oblasti polovodičů, umožňující vyšší výkon zařízení, větší funkčnost a snížené rozměry díky vertikální integraci několika polovodičových čipů v rámci jednoho balení. Jak odvětví přechází do roku 2025, několik klíčových technologických trendů formuje vývoj a přijetí stohovaných řešení.

- Pokročilá integrace přes-silikonových propojení (TSV): Technologie TSV zůstává centrálním prvkem architektur stohovaných čipů, poskytujícím vysoce husté vertikální propojení. Nedávné pokroky se zaměřují na redukci průměru a rozteče propojení, což zlepšuje integritu signálu a účinnost energie. Přední fabriky, jako jsou TSMC a Samsung Electronics, posouvají měřítka TSV, aby podpořily paměti s vysokou šířkou pásma (HBM3) a integraci logiky a paměti pro AI a HPC aplikace.

- Heterogenní integrace: Trend integrace různorodých čipů—logika, paměť, analogový a RF—v rámci jednoho stohovaného balení se zrychluje. Tento přístup umožňuje optimalizaci na systémové úrovni a podporuje rostoucí poptávku po integrovaných obvodech na míru (ASIC) v datových centrech, automobilovém průmyslu a mobilních zařízeních. Foveros od Intelu a 3D V-Cache od AMD jsou příklady komerčního přijetí heterogenního stohování.

- Balení na úrovni waferu (WLP) a technologie fan-out: Balení na úrovni waferu a technologie fan-out panelového balení získávají na popularitě díky své schopnosti poskytovat jemnější rozteče propojení a lepší tepelný výkon. ASE Technology Holding a Amkor Technology investují do pokročilých WLP linek, aby splnily poptávku po kompaktní, vysoce výkonné spotřební a automobilové elektronice.

- Inovace v oblasti správy tepla: Jak rostou výkonové hustoty, efektivní disipace tepla se stává kritickou. Nové materiály (např. diamantové kompozity, pokročilé TIM) a integrované mikrofluidní chlazení jsou zkoumány za účelem řešení tepelného zúžení v baleních s stohovanými čipy, jak je zdůrazněno v nedávných zprávách o trhu Yole Group.

- Automatizace návrhu a testovací řešení: Komplexnost architektur stohovaných čipů pohání přijetí pokročilých nástrojů pro elektronickou automatizaci návrhu (EDA) a metodologií vestavěného auto-testování (BIST). Společnosti jako Synopsys a Cadence Design Systems vyvíjejí řešení, která usnadňují návrh 3D IC, ověřování a optimalizaci výnosu.

Tyto technologické trendy by měly urychlit přijetí mikroelektronického balení stohovaných čipů v roce 2025, podporující aplikace nové generace v AI, 5G, automobilovém průmyslu a edge computingu.

Konkurenční prostředí a vedoucí hráči

Konkurenční prostředí trhu mikroelektronického balení stohovaných čipů v roce 2025 je charakterizováno intenzivními inovacemi, strategickými partnerstvími a zaměřením na pokročilé integrační technologie. Balení stohovaných čipů, které umožňuje vertikální integraci několika polovodičových čipů v rámci jednoho balení, je kritickým prvkem pro vysokovýkonné computing, mobilní zařízení a vznikající aplikace, jako je umělá inteligence (AI) a 5G komunikace.

Mezi vedoucí hráče na tomto trhu patří Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics, Intel Corporation a Amkor Technology. Tyto společnosti se etablovaly jako průkopníci v pokročilých balicích řešeních, využívající své odborné znalosti v oblasti výroby waferů, 3D integrace a systémové balení (SiP) technologií.

TSMC i nadále vede s pokročilými platformami 3D balení, jako jsou CoWoS (Chip-on-Wafer-on-Substrate) a SoIC (System on Integrated Chips), které jsou široce přijímány pro vysokovýkonné computing a AI akcelerátory. Samsung Electronics učinil významné pokroky se svou technologií X-Cube (eXtended-Cube), která umožňuje integraci vysokohustotní, vysokorychlostní paměti pro mobilní a serverové aplikace nové generace. Intel pokročuje se svou technologií 3D stohování Foveros, která umožňuje heterogenní integraci logiky a paměti, což podporuje tlak společnosti na trhy AI a datových center.

Poskytovatelé outsourcovaného montáže a testování polovodičů (OSAT), jako jsou Amkor Technology a ASE Technology Holding, jsou také klíčovými hráči, kteří nabízejí široké portfolio služeb balení stohovaných čipů fabless polovičkovým výrobcům a integrovaným výrobcům zařízení (IDM). Tito OSAT investují do pokročilých balicích linek a spolupracují s fabrikami, aby urychlili čas uvedení na trh pro komplexní řešení s více čipy.

- TSMC: Vedení v platformách CoWoS a SoIC pro AI a HPC.

- Samsung Electronics: Technologie X-Cube pro integraci paměti s vysokou šířkou pásma.

- Intel Corporation: 3D stohování Foveros pro heterogenní integraci.

- Amkor Technology a ASE Technology Holding: Pokročilé služby OSAT pro řešení stohovaných čipů.

Jak růst poptávky po miniaturizaci a výkonu narůstá, konkurenční prostředí by mělo zažít další konsolidaci, přičemž přední hráči investují významné prostředky do výzkumu a vývoje a ekosystémových partnerství, aby si udrželi technologickou výhodu v mikroelektronickém balení stohovaných čipů.

Předpovědi růstu trhu (2025–2030): CAGR, analýza příjmů a objemu

Trh s mikroelektronickým balením stohovaných čipů je připraven na robustní růst mezi lety 2025 a 2030, poháněn rostoucí poptávkou po vysokovýkonných, miniaturizovaných elektronických zařízeních v oblastech, jako je spotřební elektronika, automobilový průmysl, telekomunikace a zdravotnictví. Podle projekcí MarketsandMarkets se očekává, že globální trh 3D IC a balení stohovaných čipů zaregistruje složenou roční míru růstu (CAGR) přibližně 12–14% během tohoto období. Tato růstová trajektorie je podložena zvyšujícím se přijetím pokročilých balicích řešení, aby se vyřešily nedostatky tradičních 2D architektur, zejména pokud jde o energetickou účinnost, velikost a šířku pásma dat.

Předpovědi příjmů naznačují, že trh s mikroelektronickým balením stohovaných čipů by mohl překročit 15 miliard USD do roku 2030, z odhadovaných 7,5 miliardy USD v roce 2025. Tento nárůst je přičítán rozšíření aplikací vyžadujících vysokou hustotu integrace, jako jsou akcelerátory AI, infrastruktura 5G a zařízení edge computingu. Region Asie-Pacifik, vedený zeměmi jako Čína, Jižní Korea a Tchaj-wan, by měl dominovat podílu na trhu, přičemž více než 50% globálních příjmů pochází z této oblasti (Gartner).

Pokud jde o objem, očekává se, že počet dodávaných jednotek stohovaných čipů vzroste o CAGR 13–15% mezi lety 2025 a 2030. Tento objemový růst je poháněn rychlým nasazením chytrých telefonů nové generace, nositelných zařízení a automobilové elektroniky, které vyžadují kompaktní, vysoce výkonná balicí řešení. Mimochodem, sektor automobilového průmyslu by měl zažít nejrychlejší objemový růst, jelikož elektrická vozidla (EV) a pokročilé systémy asistence řidiče (ADAS) stále více spoléhají na architektury stohovaných čipů pro zvýšení výpočetní moci a spolehlivosti (Yole Group).

- CAGR (2025–2030): 12–14%

- Příjmy (2030): >15 miliard USD

- Objem CAGR (2025–2030): 13–15%

- Klíčové faktory růstu: AI, 5G, automobilová elektronika, miniaturizace

- Vedoucí region: Asie-Pacifik

Regionální analýza trhu: Severní Amerika, Evropa, Asie-Pacifik a zbytek světa

Globální trh s mikroelektronickým balením stohovaných čipů zažívá dynamický růst, přičemž regionální trendy formují technologické pokroky, poptávka uživatelů a vývoj dodavatelského řetězce. V roce 2025 každá z regionů Severní Amerika, Evropa, Asie-Pacifik a zbytek světa (RoW) vykazuje odlišné tržní charakteristiky a faktory růstu.

- Severní Amerika: Severní americký trh je podporován robustními investicemi do pokročilého výroby polovodičů a silnou přítomností vedoucích technologických firem. Zaměření regionu na vysokovýkonný computing, infrastrukturu 5G a automobilovou elektroniku zvyšuje poptávku po řešeních balení stohovaných čipů. Spojené státy, zejména, profitují z vládních iniciativ, které podporují domácí výrobu čipů, jak je vidět v zákoně CHIPS, který by měl urychlit přijetí pokročilých technologií balení v roce 2025 (Semiconductor Industry Association).

- Evropa: Trh mikroelektronického balení stohovaných čipů v Evropě se vyznačuje zaměřením na automobilový průmysl, průmyslovou automatizaci a IoT aplikace. Tlak regionu na technologickou suverenitu a Evropský zákon o čipech podporují investice do místních polovodičových ekosystémů. Německo a Francie vedou v oblasti výzkumu a vývoje a pilotní výroby s rostoucím důrazem na energeticky efektivní a miniaturizovaná zařízení (European Electronic Component Manufacturers Association).

- Asie-Pacifik: Asie-Pacifik zůstává největším a nejrychleji rostoucím trhem pro balení stohovaných čipů, poháněným dominancí zemí jako Čína, Jižní Korea, Tchaj-wan a Japonsko v oblasti výroby a montáže polovodičů. Rozšíření spotřební elektroniky, chytrých telefonů a zařízení umožněných AI zvyšuje poptávku. Hlavní fabriky a poskytovatelé OSAT (outsourced semiconductor assembly and test) v regionu zvyšují investice do balení 2.5D/3D a heterogenní integrace, aby splnily globální poptávku (SEMI).

- Rest of World (RoW): Ačkoli menšího rozsahu, segment RoW—včetně Latinské Ameriky, Blízkého východu a Afriky—se postupně přizpůsobuje balení stohovaných čipů, především pro telekomunikace a vznikající průmyslové aplikace. Růst je podporován zvýšenou digitalizací a vládními technologickými iniciativami, přičemž region čelí výzvám souvisejícím s infrastrukturou a kvalifikovanou pracovní silou (Gartner).

Celkově se očekává, že rok 2025 přinese pokračující regionální diverzifikaci v mikroelektronickém balení stohovaných čipů, přičemž Asie-Pacifik povede v objemu, Severní Amerika a Evropa se zaměří na inovace a strategickou autonomii a regiony RoW budou postupně zvyšovat přijetí, jak se globální digitální transformace urychluje.

Budoucí výhled: Vznikající aplikace a investiční hotspoty

Budoucí výhled pro mikroelektronické balení stohovaných čipů v roce 2025 je formován rychlými pokroky v integraci polovodičů, rozšířením AI a vysokovýkonného computing a rostoucí poptávkou po miniaturizovaných, energeticky efektivních zařízeních. Balení stohovaných čipů, které zahrnuje vertikální integraci několika polovodičových čipů v rámci jednoho balení, by mělo hrát klíčovou roli při umožnění elektroniky nové generace v několika rychle rostoucích sektorech.

Vznikající aplikace jsou zvláště prominentní v datových centrech, infrastruktuře 5G a edge computingu. Potřeba vyšší šířky pásma a nižší latence v těchto prostředích pohání přijetí 2.5D a 3D stohovaných řešení čipů, které nabízejí zlepšenou hustotu propojení a sníženou ztrátu signálu ve srovnání s tradičním balením. Například hyperskalová datová centra stále častěji využívají paměti s vysokou šířkou pásma (HBM) a stohování logiky na paměti k urychlení pracovních zátěží AI a analýzy velkých dat, což je trend zdůrazněný v nedávných analýzách od Gartner a IDC.

Spotřební elektronika, zejména chytré telefony a nositelná zařízení, zůstávají významným investičním hotspotem. Tlak na tenčí, lehčí zařízení s vylepšenou funkčností zvyšuje poptávku po pokročilých technikách balení, jako jsou přes-silikonové propojení (TSV) a balení na úrovni waferu. Podle Yole Group se očekává, že trh s balením stohovaných čipů v mobilních a IoT zařízeních zaznamená dvouciferný růst až do roku 2025, jak OEM usilují o integraci více funkcí, aniž by se zvýšila velikost zařízení.

Automobilová elektronika představuje další vznikající oblast aplikací, zejména protože elektrická vozidla (EV) a systémy autonomního řízení vyžadují kompaktní, vysoce spolehlivé výpočetní moduly. Balení stohovaných čipů umožňuje integraci senzorů, procesorů a paměti v jednom modulu, což podporuje zpracování dat v reálném čase a pokročilé systémy asistence řidiče (ADAS). McKinsey & Company odhaduje, že obsah polovodičů v automobilovém průmyslu překoná celkový růst vozidel, přičemž řešení stohovaných čipů hraje klíčovou roli.

- Klíčové investiční hotspoty pro rok 2025 zahrnují pokročilou paměť (HBM, 3D NAND), AI akcelerátory, základnové stanice 5G/6G a moduly ADAS automobilového průmyslu.

- Asie-Pacifik, vedená Tchaj-wanem a Jižní Koreou, by měla dominovat investicím do výroby a výzkumu a vývoje, jak uvádí SEMI.

- Strategická partnerství mezi fabrikami, OSAT a integrátory systémů urychlují inovace a komercializaci technologií stohovaných čipů.

Ve zkratce, mikroelektronické balení stohovaných čipů by mělo podpořit klíčové pokroky v oblasti výpočetní techniky, konektivity a mobility v roce 2025, s robustními investicemi a inovacemi zaměřenými na rychle rostoucí oblasti aplikací s vysokou hodnotou.

Výzvy, rizika a strategické příležitosti

Mikroelektronické balení stohovaných čipů, které je kritickým faktorem pro systémů s vysokou hustotou a vysokým výkonem, čelí v roce 2025 složitému souboru výzev a rizik, ale také představuje významné strategické příležitosti pro hráče v odvětví. Hlavní technickou výzvou zůstává správa tepla. Jak je více čipů vertikálně integrováno, disipace tepla se stává stále problematičtější, riskuje spolehlivost zařízení a degradaci výkonu. Pokročilé tepelné mezičlánkové materiály a inovativní návrhy rozvaděčů tepla jsou zkoumány, ale jejich integrace zvyšuje náklady a složitost výrobního procesu (SEMI).

Rizika výnosu a spolehlivosti jsou také zvýšena v architekturách stohovaných čipů. Zvýšený počet propojení, jako jsou přes-silikonová propojení (TSV), zvyšuje pravděpodobnost vad, což ovlivňuje celkový výnos. Dále mechanické napětí vyvolané během stohování a balení může vést k prasknutí čipů nebo delaminaci, zejména jak se zmenšují velikosti balení a zvyšuje se počet čipů. Tyto otázky spolehlivosti vyžadují důsledné testovací a inspekční protokoly, což může prodloužit čas uvedení na trh a zvýšit náklady (Yole Group).

Komplexita dodavatelského řetězce je dalším významným rizikem. Balení stohovaných čipů obvykle vyžaduje spolupráci mezi několika dodavateli pro výrobu waferů, ztenčení čipů, stohování a konečnou montáž. Přerušení v jakémkoli segmentu—např. nedostatek pokročilých substrátů nebo zpoždění v zařízeních pro přesné spojování—mohou mít domino efekt v časovém harmonogramu výroby. Panující geopolitické napětí a nedostatky materiálů zaznamenané v posledních letech zdůraznily zranitelnost těchto komplexních dodavatelských řetězců (Gartner).

Navzdory těmto výzvám se naskýtají strategické příležitosti. Narůstající poptávka po pamětech s vysokým pásmem, AI akcelerátorech a infrastrukturách 5G/6G pohání investice do řešení stohovaných čipů. Společnosti, které dokáží inovovat v oblastech, jako je heterogenní integrace, architektury čipů a pokročilá správa tepla, mají šanci získat významný podíl na trhu. Strategická partnerství mezi fabrikami, OSAT (outsourced semiconductor assembly and test) a poskytovateli nástrojů EDA se objevují jako klíčový faktor úspěchu, umožňující end-to-end řešení, která adresují jak technická, tak rizika dodavatelského řetězce (TSMC).

Celkově, zatímco mikroelektronické balení stohovaných čipů v roce 2025 čelí technickým, spolehlivostním a dodavatelským rizikům, také nabízí značné příležitosti k růstu pro ty, kteří jsou schopní orientovat se v neustále se vyvíjejícím prostředí s inovacemi a strategickou spoluprací.

Zdroje a odkazy

- ASE Technology Holding

- Amkor Technology

- Synopsys

- MarketsandMarkets

- Semiconductor Industry Association

- IDC

- McKinsey & Company